|

|

| Linha 30: |

Linha 30: |

| | | | |

| | ;Encontro 2 (20 fev): | | ;Encontro 2 (20 fev): |

| − | * [https://moodle.ifsc.edu.br/pluginfile.php/262427/mod_resource/content/1/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] | + | * [https://moodle.ifsc.edu.br/pluginfile.php/336168/mod_resource/content/1/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] |

| | | | |

| | * Estrutura do código VHDL | | * Estrutura do código VHDL |

Edição das 20h54min de 19 de fevereiro de 2024

Registro on-line das aulas

Unidade 1 - Aula inicial, Introdução a disciplina

| Unidade 1 - Aula inicial, Introdução a disciplina

|

- Encontro 1 (16 fev)

- A página da UC contém os materiais que não alteram entre semestre.

- Relação com as outras UCs do Eixo Sistemas Computacionais (Marrom). Ver grafo do curriculo

- ELD129002 - ELETRÔNICA DIGITAL I (ELD1): Sistema de numeração e códigos. Lógica booleana. Circuitos combinacionais. Circuitos aritméticos. Linguagem de descrição de hardware. Implementação e teste de circuitos digitais. Projeto de circuitos lógicos.

- ELD129003 - ELETRÔNICA DIGITAL II (ELD2): Dispositivos lógicos programáveis. Circuitos sequenciais. Metodologia síncrona. Projeto hierárquico e parametrizado. Máquinas de estados finita. Register Transfer Methodology. Teste de circuitos digitais. Implementação em FPGA. Introdução a Linguagem de Descrição de Hardware.

- AOC129004 - ARQUITETURA E ORGANIZAÇÃO DE COMPUTADORES (AOC): Introdução à Arquitetura Computadores. Linguagem Assembly. Linguagem de Máquina. Programação Assembly. Modos de Endereçamento. Processo de compilação e carga de um programa. Introdução à Organização de Computadores. Organização Monociclo e Multiciclo. Pipeline. Memória e Sistema de E/S.

- MIC129007 - MICROCONTROLADORES (MIC): Introdução a Microcontroladores e Aplicações. Arquitetura de um microcontrolador. Pilha e Subrotinas. Interrupção. Contadores e Temporizadores. Interface com Periféricos. Programação em alto nível (ex.: C, C++ e RUST) para Microcontroladores: Mapeamento de tipos e estruturas de alto nível para sistemas com recursos limitados. Projeto de hardware e firmware com microcontroladores.

- STE129008 - STE - SISTEMAS EMBARCADOS (STE): Conceitos em Sistemas Embarcados. Metodologia de Desenvolvimento de Sistemas Embarcados. Sistemas Operacionais para Sistemas Embarcados. Ferramentas de desenvolvimento e depuração. Barramentos e dispositivos de acesso a redes. Desenvolvimento de Projeto.

- Nesta página está o Registro diário dos encontros e avaliações.

- A entrega de atividades e avaliações será através da plataforma Moodle. A inscrição dos alunos é automática a partir do SIGAA.

- Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o chat institucional. A princípio todos os alunos já estão previamente cadastrados pelo seu email institucional. Confiram enviando uma mensagem de apresentação.

- Utilizaremos durante as aulas algumas ferramentas computacionas como o site do Falstad para entender circuitos digitais e fazer simulações básicas.

- Também utilizaremos os softwares Quartus Light e ModelSim instalados nas maquinas do laboratório para praticar a parte de programação de hardware (descrição de hardware). Esses softwares também podem ser usados através da Nuvem do IFSC..

- LER PARA O PRÓXIMO ENCONTRO

- Revisão dos conceitos sobre circuitos combinacionais vistos em CIL/ELD1

- Para alunos que não cursaram ELD1 (não conhecem VHDL), irei fornecer uma sequência de estudos para conhecer melhor as instruções concorrentes do VHDL.

- Ler Introdução a linguagem de descrição de hardware (DHL)

|

Unidade REV - PRIMEIRO CONTATO COM VHDL

| Unidade REV - PRIMEIRO CONTATO COM VHDL

|

- Encontro 2 (20 fev)

- Declaração das bibliotecas e pacotes LIBRARY / PACKAGE

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

- Exemplo - Declaração de uma porta NAND em VHDL

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

Uso do ambiente EDA - QUARTUS Prime para programação em VHDL.

- PASSO 0

Acesse a nuvem do IFSC usando um terminal via ssh:

USER=LOGIN_SIGAA

ssh $USER@quartus.sj.ifsc.edu.br -XC

Insira a senha do SIGAA

LOGIN_SIGAA@quartus.sj.ifsc.edu.br's password:

- PASSO 1

Abra o Quartus Prime digitando no terminal

quartus20.1.sh

Em seguida abra um arquivo para inserir o código VHDL. No menu superior selecione [File > New > Design Files: VHDL File] e [OK]

- PASSO 2

- Copie o código VHDL acima para o espaço de edição e salve o arquivo com o nome da entity: nand_gate.vhd, em um pasta exclusiva para este projeto.

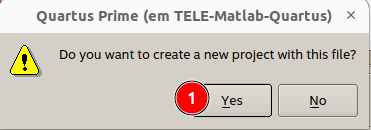

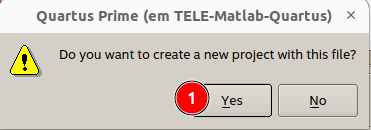

- Ao ser perguntado se deseja criar um novo projeto, responda [Yes]

- Os próximos passos podem ser realizados da seguinte forma:

- Na tela Introduction [Next >]

- Na tela Directory, Name, Top-Level Entity

- Anote onde o projeto será salvo.

/home/USER/PASTA_DO_PROJETO/

- Se quiser, troque a pasta clicando sobre os [...] e selecionando/criando a pasta onde o projeto será salvo.

- Recomendamos que no início você salve cada projeto em uma pasta separada.

- Note o nome do projeto. Se quiser pode mudá-lo

nand_gate

- Note o nome da top-level design entity

nand_gate

- Em seguida clique em [Next >]

- Na tela Project Type clique em [Next >]

- Na tela Add Filesclique em [Next >], pois note que seu arquivo "nand_gate.vhd" já está na lista dos arquivos do projeto.

- Na tela Family, Device & Board Settings, escolha a Family = [Cyclone IV E] e o Device = [EP4CE6E22A7] e clique em [Next >]

- Na tela EDA Tool Setting [Next >]

- Note na tela Summary os dados do projeto e clique [Finish]

- PASSO 3

Realize a Analysis & Synthesis [Processing > Start > Start Analysis & Synthesis], ou use um dos botões que o professor mostrou em aula.

- Analise o Compilation Report.

1) Qual é a Top-level Entity? ___________________________

2) Quantos elementos lógicos foram utilizados? ___________________________

3) Quantos pinos foram utilizados? ___________________________

4) Algum outro dado está diferente de zero? Quais? ___________________________

- PASSO 4

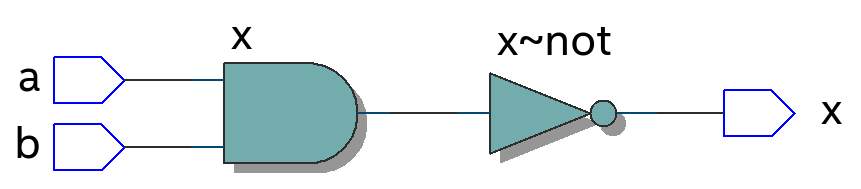

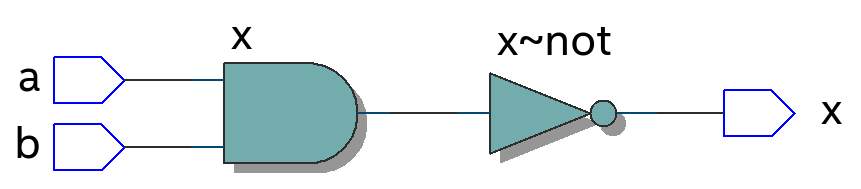

- Use o RTL Viewer para ver a descrição RTL do circuito. Selecione [Tools > Netlist Vieweres > RTL Viewer].

- Analise o Diagrama RTL, e note que ele representa a implementação de uma porta AND seguida de um NOT.

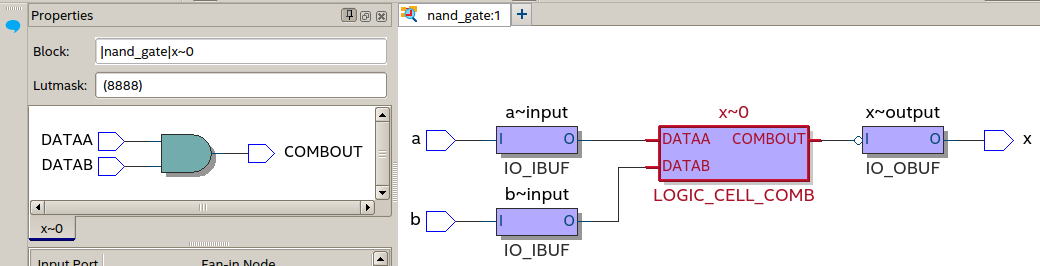

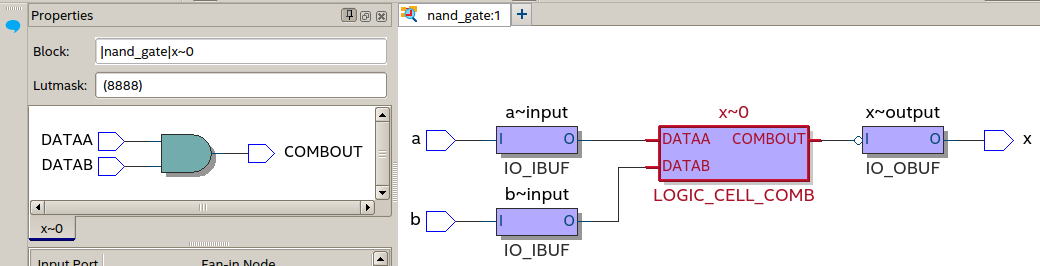

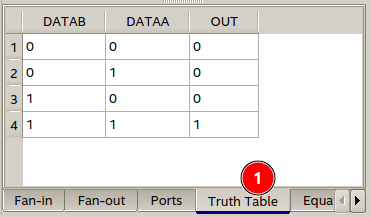

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado. Selecione [Tools > Netlist Vieweres > Technology Map Viewer (Post-Mapping)]. Ao abrir, clique direito sobre o símbolo LOGIC_CELL_COMB e selecione Properties para visualizar o que está implementado.

- Analise o Technolgy Map, e busque perceber que ele representa a mesma implementação de uma porta AND seguida de um NOT (onde está o NOT?).

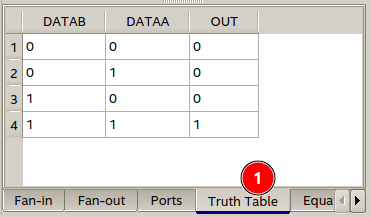

- Lembre-se que apenas um circuito equivalente é mostrado, pois na prática essa célula contém uma LUT, o que corresponde a implementar diretamente a tabela verdade.

- Note que a tabela verdade mostrada corresponde novamente a uma porta AND.

- PASSO 5

- Modifique a descrição do circuito para implementar o circuito da função Y = (A.B)' + C.D'B', salve o projeto Ckt2.vhd e de o mesmo nome para a entity.

- LER PARA O PRÓXIMO ENCONTRO

|

Avaliações

Durante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - :

- A2 - :

- A3 - :

- A4 - :

- R - Recuperação de A1 a A4 :

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo.

Referências Bibliográficas:

Curso de Engenharia de Telecomunicações