Mudanças entre as edições de "MIC29004-2019-2"

| Linha 153: | Linha 153: | ||

*'''Objetivos:''' | *'''Objetivos:''' | ||

**Entender as mudanças da arquitetura e da organização do BIP II | **Entender as mudanças da arquitetura e da organização do BIP II | ||

| + | |||

| + | |||

| + | *'''Experimento:''' | ||

| + | ** **[http://docente.ifsc.edu.br/roberto.matos/mic_public/labs/lab1-memoria.zip Instruções de Desvio BIP II] | ||

| + | |||

| + | |||

| + | |||

*'''Exercício:''' | *'''Exercício:''' | ||

| Linha 160: | Linha 167: | ||

** Trabalho em Dupla | ** Trabalho em Dupla | ||

** Entrega 08/09 e Apresentação 10/09 | ** Entrega 08/09 e Apresentação 10/09 | ||

| − | |||

= Aula 03/09/2019: Dúvidas Lista de Exercício e Apoio Trabalho BIP II = | = Aula 03/09/2019: Dúvidas Lista de Exercício e Apoio Trabalho BIP II = | ||

Edição das 10h08min de 2 de setembro de 2019

Microprocessadores: Diário de Aula 2019-2

- Professor: Roberto de Matos

- Encontros: 2ª e 3ª feira às 9:40h

- Atendimento Paralelo: 4ª às 10h e 14h (1h cada)

- Plano de Ensino

- Cronograma de Aulas

- Notas

Material

Listas de Exercício

- Lista de Exercícios: Memória, Arquitetura, Organização e BIP

- Lista Introdução a programação do BIP

- Lista de Exercícios Microcontroladores e AVR

Aula 29/07/2019: Apresentação

- Apresentação do professor.

- Apresentação da disciplina: conteúdo, bibliografia e avaliação.

Aula 30/07/2019: Introdução sobre Memória

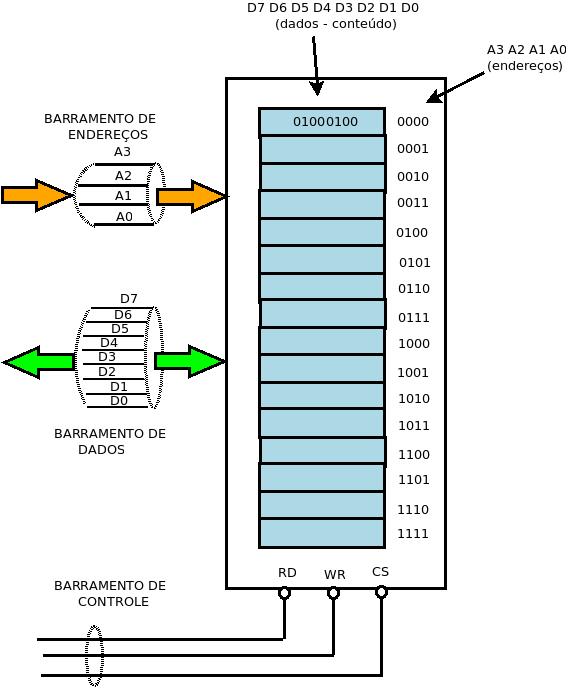

Diagrama em blocos da memória e barramentos

No diagrama abaixo está representado um bloco de memória primária de 16x8 (dezesseis endereços por 8 bits).

- Note que uma posição de memória pode ser vista como uma caixa que possue um endereço e um conteúdo.

- O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits.

Para que us dispositivo externo possa "acessar" a memória para leitura ou escrita, ele deve se utilizar de um conjunto de fios que chamamos de barramentos.

Barramento de Endereços

Este barramento permite determinar o endereço de uma posição a ser acessada na memória. Um barramento de 4 linhas de endereço é designado por A3,A2,A1 e A0.

Supondo uma memória com endereços designados da forma hexadecimal de 0h a Fh. Supondo que A3 seja associado ao bit mais significativo e A0 ao bit menos significativo. Então, para acessar a posição Bh de memória, deve-se injetar A3=1, A2=0, A1=1 e A0=1. Note que

O termo "injetar" significa aqui que um dispositivo externo deve forçar tensão nas linhas do barramento. Esta tensão depende da tecnologia utilizada. Poderia ser, por exemplo, 5V para o nível lógico 1 e 0V par ao nível lógico 0.,

Aula 04/08/2019: Laboratório de Memória - Introdução

- Notas de Aula:

- Experimento 1 - Memória 16x4:

- Entrar no Windows.

- Baixar o arquivo de projeto aqui. Coloque em um diretório conhecido.

- Descompacte. Clique sobre o arquivo *.pdsprj. O PROTEUS será executado e o projeto aberto.

- Observe que o projeto está parcialmente pronto. Você pode entrar em modo simulação.

- O sistema está preparado para que se possa inserir ou ler manualmente posições de memória.

- Leia todas as 16 posições de memória e anote os valores.

- Grave o número da sua matrícula na memória. Preencha o restante com zero.

- Note o Chip Select está habilitado sempre. Coloque uma chave adicional para colocar o Chip Select.

- Atividade 1 - Associação de Memórias:

- Usando como referência o experimento 1 e os exemplos de associação de memória vistos em sala de aula, implemente o seguinte:

- Uma memória 16x8

- Uma memória 64x4

- Uma memória 64x8

- Entrega:

- Fazer em Duplas

- Última Aula de dúvidas: 06/08 (segunda)

- Apresentação: 07/08 (terça)

Aula 12/08/2019: Laboratório de Memória - Associação

- Finalizar o Exercício

Aula 13/08/2019: Introdução à Arquitetura e Organização de Computadores

- Objetivos:

- Introdução a Microprocessadores

- Notas de Aula:

- Experimento:

Aula 19/08/2019: Arquitetura BIP

- Objetivos:

- Entender a Arquitetura BIP

- Programar em Assembly o BIP

- Notas de Aula:

- Experimento:

Aula 20/08/2019: Organização do BIP

- Objetivos:

- Entender a Organização do BIP

- Criar tabela de decodificação do BIP

- Notas de Aula:

- Software Utilizado:

Aula 26/08/2019: Decodificador BIP

- Objetivos:

- Entender a execução do BIP passo-a-passo no Proteus

- Implementar o circuito decodificador do BIP no Proteus

- Entender as mudanças da arquitetura e da organização do BIP II

- Experimento:

Aula 27/08/2019: Decodificador BIP (cont.) e BIP II

- Objetivos:

- Finalizar o Decode do BIP

- Introdução da arquitetura do BIP II

- Exercícios:

- Implementar e simular exemplos com as instruções de desvio do BIP II

Aula 02/09/2019: Organização do BIP II

- Objetivos:

- Entender as mudanças da arquitetura e da organização do BIP II

- Experimento:

- Exercício:

- Implementar as mudanças da organização do BIP para criar o BIP II

- Implementar o decodificador do BIP II

- Implementar programas de testes no assembly do BIP II

- Trabalho em Dupla

- Entrega 08/09 e Apresentação 10/09

Aula 03/09/2019: Dúvidas Lista de Exercício e Apoio Trabalho BIP II

- Objetivos:

- Aula de dúvidas

- Objetivos:

- Dúvidas da Lista de Exercícios: Memória, Arquitetura, Organização e BIP para prova I.

Aula 09/09/2019: Prova I

- Objetivos:

- Avaliação dos conceitos de Memória, Arquitetura e Organização, BIP I e II

Aula 10/09/2019: Correção da Prova e Trabalho BIP II

- Objetivos:

- Correção da avaliação para completar o processo de ensino-aprendizagem.

- Apresentação do Trabalho BIP II