Mudanças entre as edições de "DIG222802 AULA04"

| Linha 15: | Linha 15: | ||

<math>A_T=t_{pd}(FF)+t_{pd}(AND)\,</math> | <math>A_T=t_{pd}(FF)+t_{pd}(AND)\,</math> | ||

| + | |||

| + | |||

| + | Desta forma nesse tipo de contador o atraso não depende do número de bits, mas apenas da tecnologia utilizada. Por outro lado, como o atraso de propagação é menor, o contador síncrono pode trabalhar com frequências maiores que o contador assíncrono. | ||

| + | |||

| + | |||

| + | ==Contadores síncronos decrescentes== | ||

| + | |||

| + | Do mesmo modo que os contadores assíncronos, os contadores síncronos podem contar de forma decrescente. Para isso devemos usar as saídas <math>\bar Q</math> no lugar vez das saídas Q na lógica de habilitação das entradas J e K. Também devemos pegar o sinal de ABCD das portas <math>\bar Q</math>. | ||

| + | |||

| + | (simulado em sala de aula) | ||

=Lista de Exercícios= | =Lista de Exercícios= | ||

Edição das 16h46min de 20 de abril de 2016

Contadores síncronos

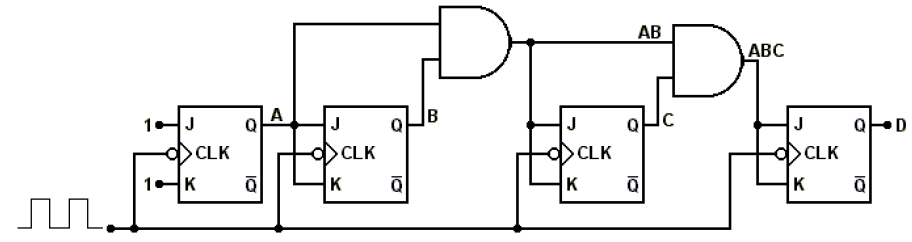

Como vimos, o atraso de propagação dos FF nos contadores assíncronos limita a sua frequência máxima. Esse problema pode ser resolvido fazendo com que os FF mudem o estado de suas saídas no momento em que ocorre a transição de clock. Essa configuração caracteriza os contadores chamados de síncronos e é mostrada na Figura 1.

Figura 1 - Contador síncrono ascendente.

A análise da lógica do circuito do contador mostra que os FF do tipo JK somente estão no estado TOOGLE (J = 1 e K = 1) quando todas as saídas dos FF anteriores estão em nível ALTO. Como o sinal de clock é comum a todos os FF, o atraso de propagação do contador será o atraso de um FF somado ao atraso das portas AND.

- Atraso total ()

Desta forma nesse tipo de contador o atraso não depende do número de bits, mas apenas da tecnologia utilizada. Por outro lado, como o atraso de propagação é menor, o contador síncrono pode trabalhar com frequências maiores que o contador assíncrono.

Contadores síncronos decrescentes

Do mesmo modo que os contadores assíncronos, os contadores síncronos podem contar de forma decrescente. Para isso devemos usar as saídas no lugar vez das saídas Q na lógica de habilitação das entradas J e K. Também devemos pegar o sinal de ABCD das portas .

(simulado em sala de aula)

Lista de Exercícios

http://wiki.sj.ifsc.edu.br/images/2/2a/EX1_DIG222802.pdf

Referências

[1] Apostila do CURSO DE ELETRÔNICA DIGITAL. CEFET/SC: São José, 2011.

| << | <> | >> |

|---|