|

|

| Linha 341: |

Linha 341: |

| | | | |

| | | | |

| | + | ;Tabela verdade: |

| | + | [[Arquivo:tabela6.jpg]] |

| | | | |

| | + | *A = Toca-discos |

| | + | *B = Toca-fitas |

| | + | *C = Rádio FM |

| | + | *S = Saída em forma de vetor (da esquerda para a direita mostra a ordem e preferência= A,B,C) |

| | | | |

| | + | ;Wave Form: |

| | + | [[Arquivo:wave6.jpg|1070px|thumb|left]] |

| | | | |

| | | | |

Edição das 20h42min de 13 de abril de 2015

Relatório referente a Avaliação 1:

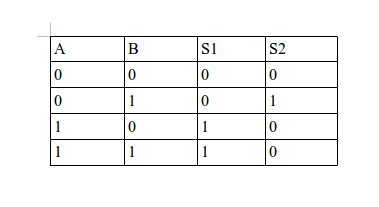

1 - Cruzamento de duas ruas

Desenvolver um sistema automático para os semáforos em um cruzamento de duas ruas, com as seguintes características:

1- Quando houver carros somente na rua B, o semáforo 2 deverá permanecer verde

2- Quando houver carros somente na rua A, o semáforo 1 deverá permanecer verde

3- Quando houver carros nas duas ruas, o semáforo 1 deverá permanecer verde

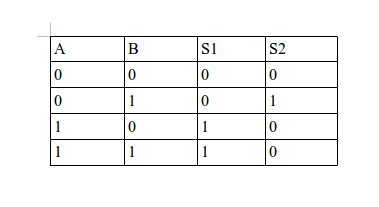

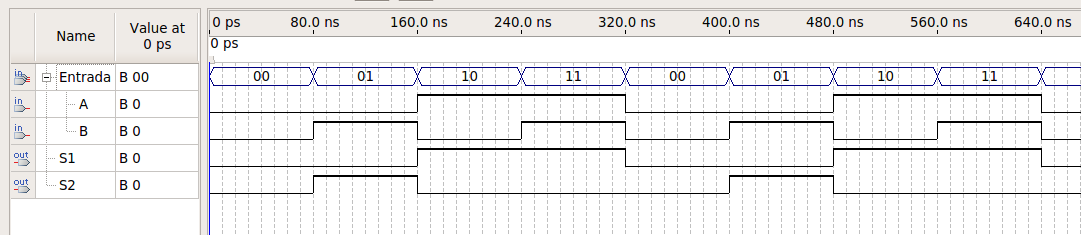

- Tabela verdade

- A = 0 - não possui carro na rua A

- A = 1 - possui carro na rua A

- B = 0 - não possui carro na rua B

- B = 1 - possui carro na rua B

- S1 = 0 - sinaleira da rua A fechada

- S1 = 1 - sinaleira da rua A aberta

- S2 = 0 - sinaleira da rua B fechada

- S2 = 1 - sinaleira da rua B aberta

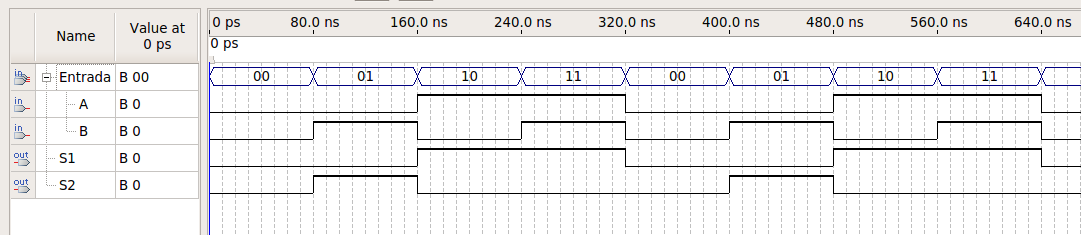

- Wave Form

- Método adotado

Behavioral if

Utilizamos esse modelo pois era um código com poucas entradas e saídas. Dessa forma ficou mais simples e fácil de entender.

| Código VHDL - Clicar no "+" para expandir

|

library IEEE;

use IEEE.std_logic_1164.all;

entity prova is

port (A, B, C, POWER: in STD_LOGIC;

VALVULA_1, VALVULA_2, LED, LED_ERRO: out STD_LOGIC);

end prova;

architecture exercicio5 of prova is

signal ABC : std_logic_vector (2 downto 0);

begin

ABC <= A&B&C;

vazao : process(ABC) is

begin

if POWER = '0' then

LED <= '0';

case(ABC) is

when "001" =>

VALVULA_1 <= '1';

VALVULA_2 <= '0';

LED_ERRO <= '0';

when "011" =>

VALVULA_1 <= '0';

VALVULA_2 <= '0';

LED_ERRO <= '0';

when "111" =>

VALVULA_1 <= '0';

VALVULA_2 <= '1';

LED_ERRO <= '0';

when others =>

LED_ERRO <= '1';

VALVULA_1 <= '0';

VALVULA_2 <= '0';

end case;

else

VALVULA_1 <= '0';

VALVULA_2 <= '1';

LED <= '1';

end if;

end process vazao;

end exercicio5;

|

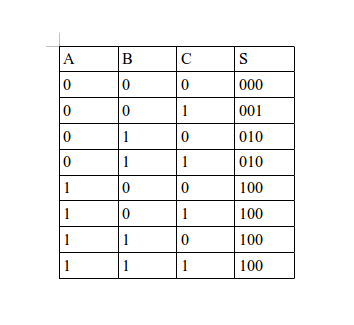

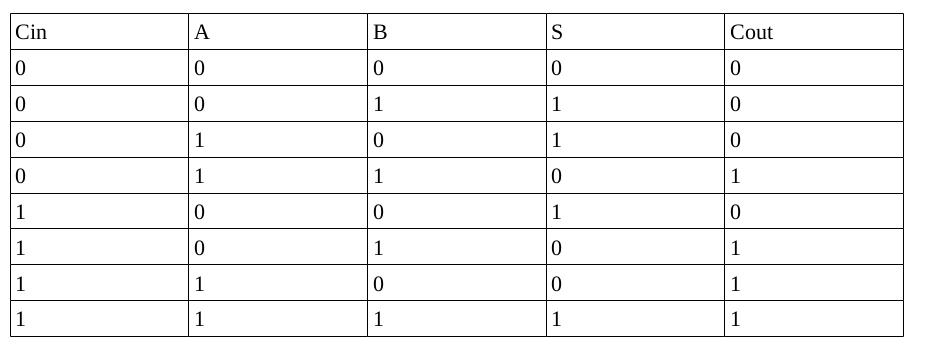

2 - Um amplificador e três aparelhos

Desenvolver um sistema que comuta a utilização de um amplificador para três aparelhos, obedecendo as seguintes prioridades:

1- Toca-discos

2- Toca-fitas

3- Rádio FM

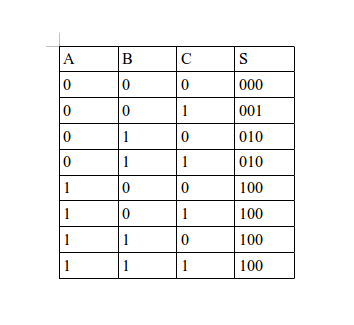

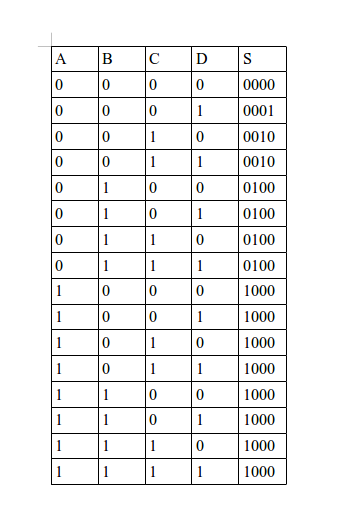

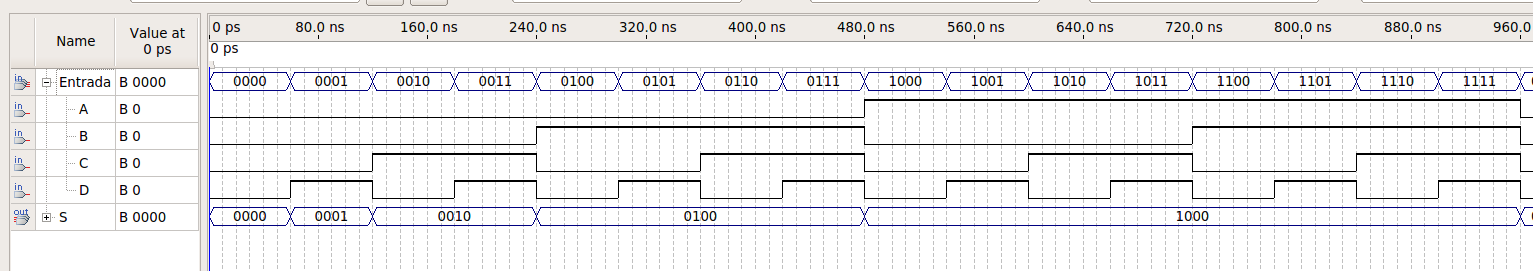

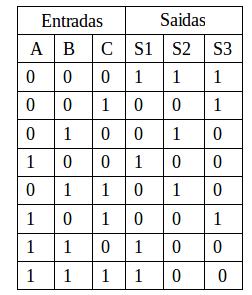

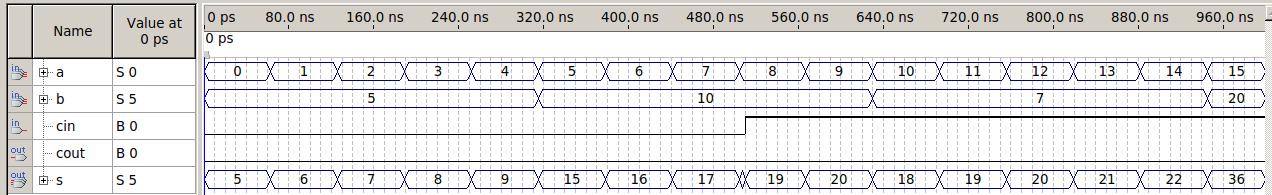

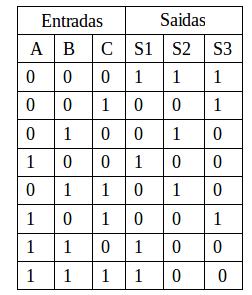

- Tabela verdade

- A = Toca-discos

- B = Toca-fitas

- C = Rádio FM

- S = Saída em forma de vetor (da esquerda para a direita mostra a ordem e preferência= A,B,C)

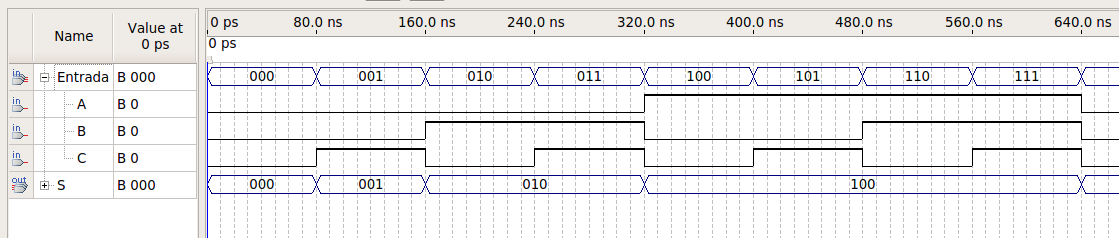

- Wave Form

- Método adotado

Behavioral case

Utilizamos esse modelo pois esse código já possuia 3 entradas, portanto a tabela verdade fica um pouco maior. Dessa forma ficou um código menor e mais simples.

| Código VHDL - Clicar no "+" para expandir

|

library IEEE;

use IEEE.std_logic_1164.all;

entity prova is

port (A, B, C : in STD_LOGIC;

S : out STD_LOGIC_vector (2 downto 0));

end prova;

architecture exercicio2 of prova is

signal ABC : std_logic_vector (2 downto 0);

begin

ABC <= A & B & C;

amplifica : process(ABC) is

begin

case(ABC) is

when "001" => S <= "001";

when "010" => S <= "010";

when "011" => S <= "010";

when "100" => S <= "100";

when "101" => S <= "100";

when "110" => S <= "100";

when "111" => S <= "100";

when others => S <= "000";

end case;

end process amplifica;

end exercicio2;

|

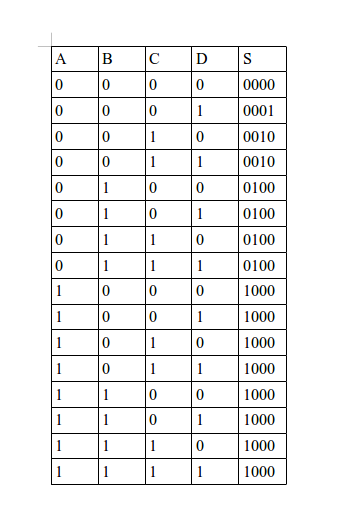

3 - Intercomunicadores

Desenvolver um sistema que comuta intercomunicadores em uma empresa, obedecendo as seguintes prioridades:

1- Presidente

2- Vice-presidente

3- Engenharia

4- Chefe de seção

- Tabela verdade

- A = Presidente

- B = Vice-presidente

- C = Engenharia

- D = Chefe de seção

- S = Saída em forma de vetor (da esquerda para a direita mostra a ordem e preferência = A,B,C,D)

- Wave Form

- Método adotado

Behavioral case

Utilizamos esse código por ter 4 entradas e porque foi o método que ficou mais claro e simples para o grupo.

| Código VHDL - Clicar no "+" para expandir

|

library IEEE;

use IEEE.std_logic_1164.all;

entity prova is

port (A, B, C, D : in STD_LOGIC;

S : out STD_LOGIC_vector (3 downto 0));

end prova;

architecture exercicio3 of prova is

signal ABCD : std_logic_vector (3 downto 0);

begin

ABCD <= A & B & C & D;

amplifica : process(ABCD) is

begin

case(ABCD) is

when "0001" => S <= "0001";

when "0010" => S <= "0010";

when "0011" => S <= "0010";

when "0100" => S <= "0100";

when "0101" => S <= "0100";

when "0110" => S <= "0100";

when "0111" => S <= "0100";

when "1000" => S <= "1000";

when "1001" => S <= "1000";

when "1011" => S <= "1000";

when "1100" => S <= "1000";

when "1101" => S <= "1000";

when "1110" => S <= "1000";

when "1111" => S <= "1000";

when others => S <= "0000";

end case;

end process amplifica;

end exercicio3;

|

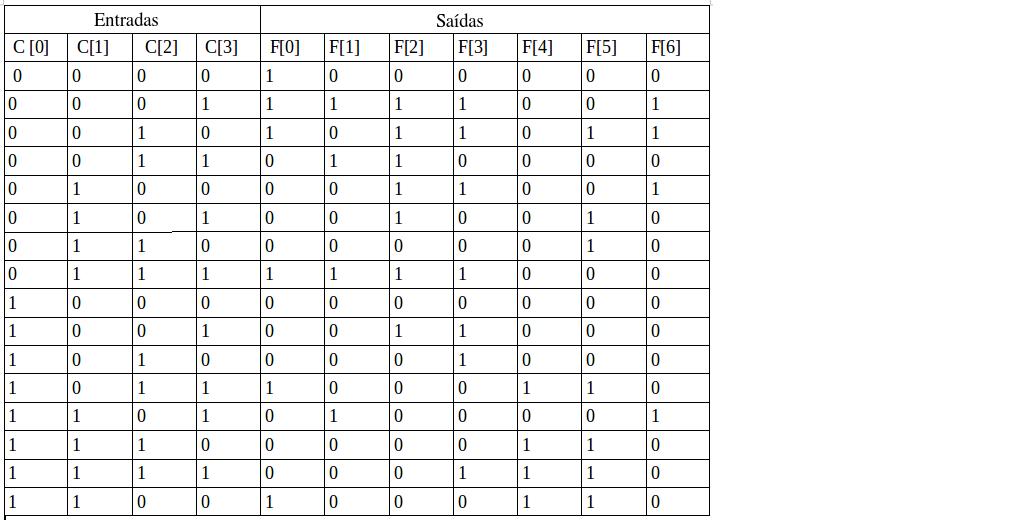

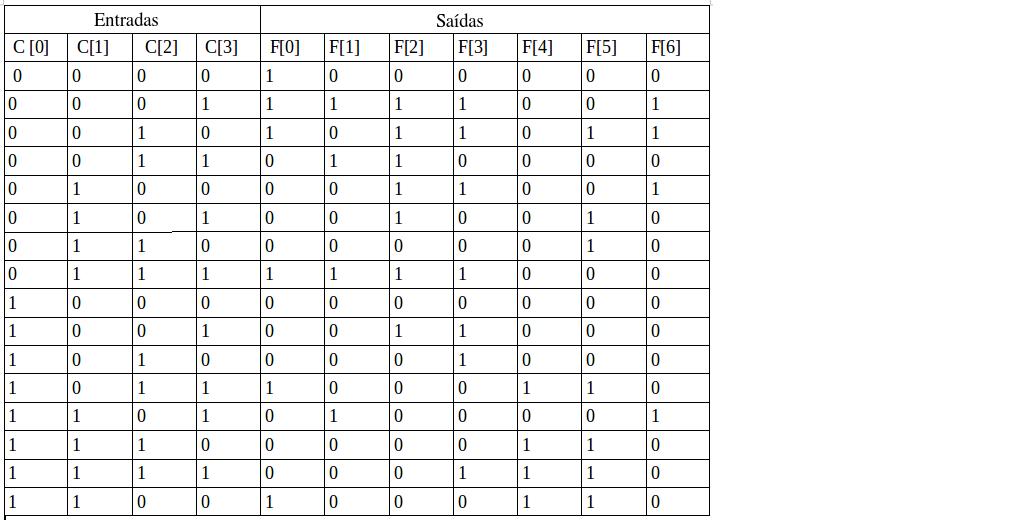

4 - Display de 7 segmentos

Desenvolver um sistema que mostra um número hexadecimal num display de 7 segmentos

- Tabela verdade

- Wave Form

Arquivo:Exercicio4.jpg

- Método utilizado

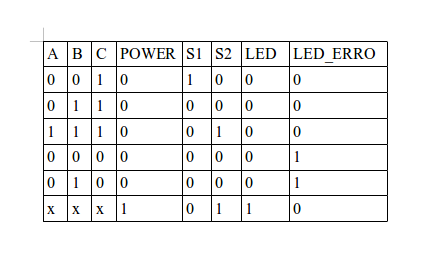

5 - Tanque com fluido

Desenvolver um sistema para controlar o nível de fluido em um tanque por meio de uma válvula de entrada e uma válvula de saída, de igual vazão. O nível de fluído deve ser mantido entre dois níveis, medidos com dois sensores, um de mínimo e outro de máximo. Um botão para total esvaziamento do tanque (equivalente à um botão de liga/desliga do tanque) deve ser previsto.

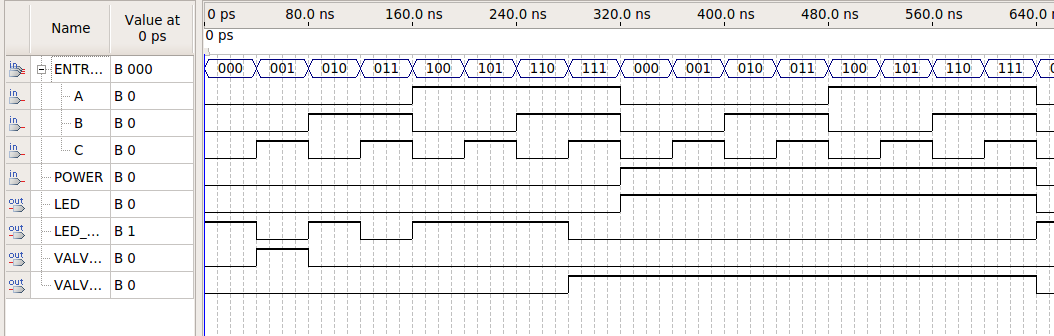

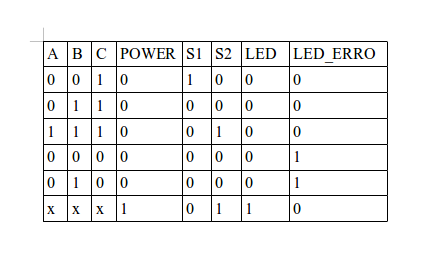

- Tabela verdade

- 001 - nível mínimo

- 011 - nível médio

- 111 - tanque cheio

- Power = 0 - sistema funcionando

- Power = 1 - esvaziamento do tanque (não importa os valores de A,B,C)

- LED = aceso mostra que Power está em 1

- LED_ERRO = aceso quando a entrada não for nenhuma das possíveis

- Obs: Foi colocado somente 2 exemplos de erro na tabela

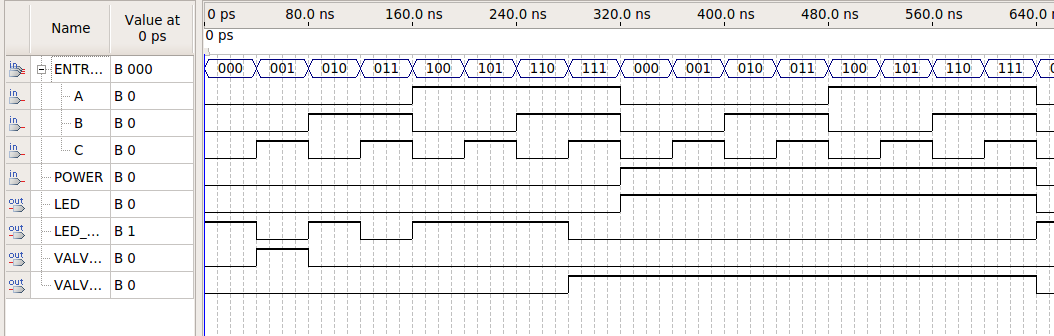

- Wave Form

- Método utilizado

Behavioral case

Foi o mais simples e rápido de fazer, pois colocamos somente os casos de entrada possíveis e as demais colocamos como erro.

| Código VHDL - Clicar no "+" para expandir

|

library IEEE;

use IEEE.std_logic_1164.all;

entity prova is

port (A, B, C, POWER: in STD_LOGIC;

VALVULA_1, VALVULA_2, LED, LED_ERRO: out STD_LOGIC);

end prova;

architecture exercicio5 of prova is

signal ABC : std_logic_vector (2 downto 0);

begin

ABC <= A&B&C;

vazao : process(ABC) is

begin

if POWER = '0' then

LED <= '0';

case(ABC) is

when "001" =>

VALVULA_1 <= '1';

VALVULA_2 <= '0';

LED_ERRO <= '0';

when "011" =>

VALVULA_1 <= '0';

VALVULA_2 <= '0';

LED_ERRO <= '0';

when "111" =>

VALVULA_1 <= '0';

VALVULA_2 <= '1';

LED_ERRO <= '0';

when others =>

LED_ERRO <= '1';

VALVULA_1 <= '0';

VALVULA_2 <= '0';

end case;

else

VALVULA_1 <= '0';

VALVULA_2 <= '1';

LED <= '1';

end if;

end process vazao;

end exercicio5;

|

6 -Cruzamento de três ruas

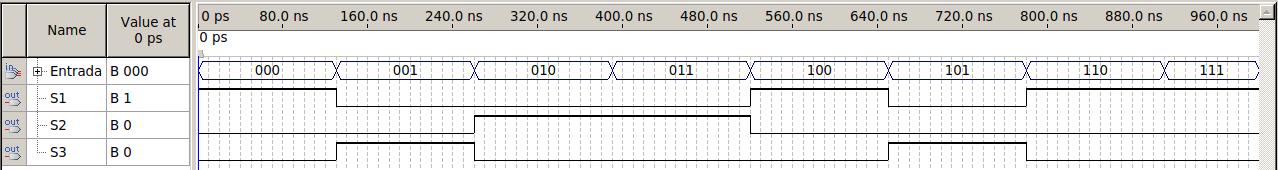

- Tabela verdade

- A = Toca-discos

- B = Toca-fitas

- C = Rádio FM

- S = Saída em forma de vetor (da esquerda para a direita mostra a ordem e preferência= A,B,C)

- Wave Form

| Código VHDL - Clicar no "+" para expandir

|

library IEEE;

use IEEE.std_logic_1164.all;

entity prova is

port (A, B, C : in STD_LOGIC;

S1, S2, S3 : out STD_LOGIC);

end prova;

architecture exercicio6 of prova is

begin

sinal : process(A,B,C) is

begin

if (A = '0' and B = '0' and C = '1') then

S1 <= '0';

S2 <= '0';

S3 <= '1';

elsif (A = '0' and B = '1' and C = '0') then

S1 <= '0';

S2 <= '1';

S3 <= '0';

elsif (A = '1' and B = '0' and C = '0') then

S1 <= '1';

S2 <= '0';

S3 <= '0';

elsif (A = '1' and B = '0' and C = '1') then

S1 <= '0';

S2 <= '0';

S3 <= '1';

elsif (A = '1' and B = '1' and C = '0') then

S1 <= '1';

S2 <= '0';

S3 <= '0';

elsif (A = '0' and B = '1' and C = '1') then

S1 <= '0';

S2 <= '1';

S3 <= '0';

else

S1 <= '1';

S2 <= '0';

S3 <= '0';

end if;

end process sinal;

end exercicio6;

|

7 - Tanque de dois níveis, com sensor de temperatura

| Código VHDL - Clicar no "+" para expandir

|

library IEEE;

use IEEE.std_logic_1164.all;

entity prova is

Port ( A, B, C, D, E, POWER : in std_logic;

TEMP : in std_logic_vector(1 downto 0);

V1, V2, ERRO, AGUAFRIA, AGUAQUENTE : out std_logic);

end entity;

architecture exercicio7 of prova is

signal ABCDE : std_logic_vector (4 downto 0);

begin

ABCDE <= A&B&C&D&E;

vazao : process(ABCDE)

begin

if POWER = '1' then

case (ABCDE) is

when "00101" =>

V1 <= '1';

V2 <= '1';

ERRO <= '0';

when "01101" =>

V1 <= '1';

V2 <= '1';

ERRO <= '0';

when "11101" =>

V1 <= '1';

V2 <= '1';

ERRO <= '0';

when "00111" =>

V1 <= '1';

V2 <= '0';

ERRO <= '0';

when "01111" =>

V1 <= '1';

V2 <= '0';

ERRO <= '0';

when "11111" =>

V1 <= '0';

V2 <= '0';

ERRO <= '0';

when others =>

ERRO <= '1';

V1 <= '0';

V2 <= '0';

end case;

else

ERRO <= '0';

V1 <= '0';

V2 <= '0';

AGUAQUENTE <= '0';

AGUAFRIA <= '0';

end if;

if TEMP = "00" then

AGUAFRIA <= '1';

AGUAQUENTE <='0';

elsif TEMP = "11" then

AGUAQUENTE <= '1';

AGUAFRIA <= '0';

elsif TEMP = "01" then

AGUAQUENTE <= '0';

AGUAFRIA <= '0';

elsif TEMP = "10" then

AGUAQUENTE <= '0';

AGUAFRIA <= '0';

end if;

end process;

end exercicio7;

|

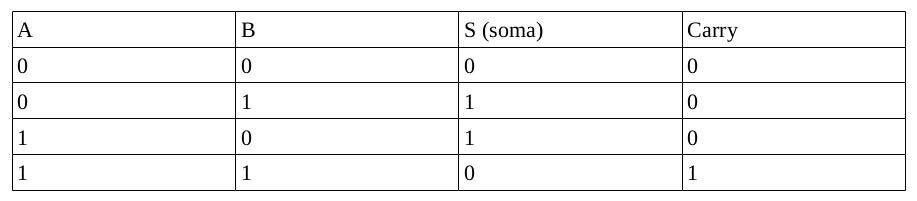

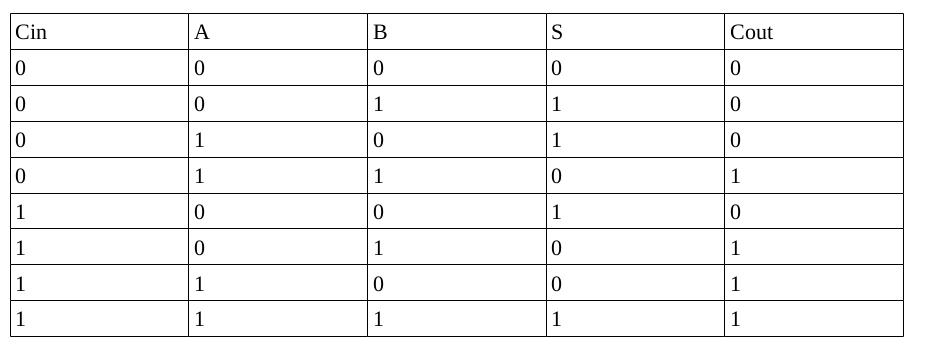

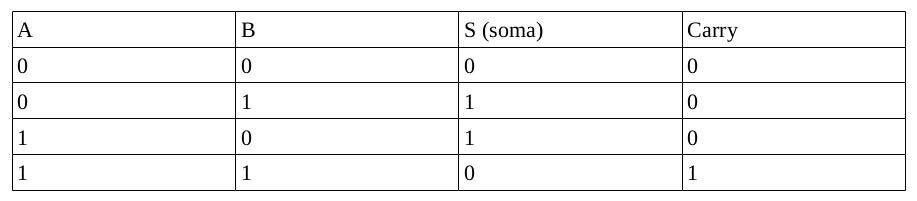

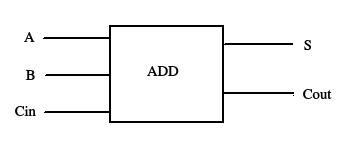

8 - Somador de 8 bits

Supondo a soma de dois bits, para cada par de bit somado existem duas saídas: o vai um (carry) e o resultado da soma.

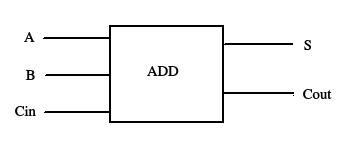

- Tabela verdade

Pela tabela verdade podemos concluir que S e carry podem ser calculados por uma porta XOR e uma porta AND, respectivamente.

S = B xor B

Carry = A and B

- Somador Completo

O circuito capaz de realizar a soma de 3 bits (A,B e Cin) dois significativos e um de transporte, gerando o resultado em dois bits ( S e Cout) é denominado somador completo. A entrada Cin (bit Carry de entrada) recebe o transporte da soma do estagio anterior (carry).

- Tabela verdade

S = A xor B xor Cin

Cout = (A and B) or (B and Cin) or (A and Cin)

Um somador de 8 bits basicamente são 8 somadores de 1 bit

- Wave Form

Método utilizado

Data-Flow

Foi o mais simples e rápido de fazer.

| Código VHDL - Clicar no "+" para expandir

|

library IEEE;

use IEEE.std_logic_1164.all;

entity prova is

port (

cin: in STD_LOGIC;

a,b: in STD_LOGIC_VECTOR(7 DOWNTO 0);

cout: out STD_LOGIC;

s: out STD_LOGIC_VECTOR(7 DOWNTO 0));

end prova;

architecture exericio8 of prova is

begin

process(a,b,cin)

variable soma: std_logic_vector(7 downto 0);

variable c: std_logic;

begin

c := cin;

for i in 0 to 7 loop

soma(i) := a(i) xor b(i) xor c;

c := (a(i) and b(i)) or ((a(i) xor b(i)) and c);

end loop;

cout <= c;

s <= soma;

end process;

end exericio8;

|