Mudanças entre as edições de "Circuitos Lógicos Aritméticos"

Ir para navegação

Ir para pesquisar

| Linha 25: | Linha 25: | ||

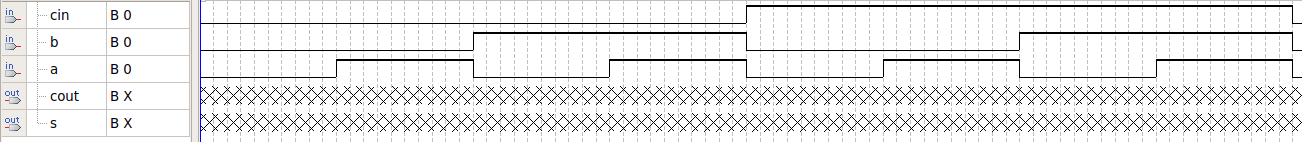

[[Arquivo:FA-SIM.png|800 px]] | [[Arquivo:FA-SIM.png|800 px]] | ||

*Analise o resultado preenchendo a tabela-verdade abaixo: | *Analise o resultado preenchendo a tabela-verdade abaixo: | ||

| + | |||

| + | <center> | ||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | ! colspan="3" style="background: #efefef;" | Entradas | ||

| + | ! colspan="2" style="background: #ffdead;" | Saídas | ||

| + | |- | ||

| + | !width="40"| cin | ||

| + | !width="40"| a | ||

| + | !width="40"| b | ||

| + | !width="40"| s | ||

| + | !width="40"| cout | ||

| + | |- | ||

| + | | 0 || 0 || 0 || || | | ||

| + | |- | ||

| + | | 0 || 0 || 1 || || | | ||

| + | |- | ||

| + | | 0 || 1 || 0 || || | | ||

| + | |- | ||

| + | | 0 || 1 || 1 || || | | ||

| + | |- | ||

| + | | 1 || 0 || 0 || || | | ||

| + | |- | ||

| + | | 1 || 0 || 1 || || | | ||

| + | |- | ||

| + | | 1 || 1 || 0 || || | | ||

| + | |- | ||

| + | | 1 || 1 || 1 || || | | ||

| + | |} | ||

| + | </center> | ||

Edição das 18h56min de 5 de junho de 2014

Objetivos

- Construir testar um circuito somador completo (FA -full adder) a partir de portas lógicas usando o diagrama esquemático do QUARTUS II.

- Fazer a simulação funcional do circuito com o QSIM

- Construir um somador de 4 bits usando os FA como subcircuito.

- Construir um multiplicador de 4 bits usando os FA como subcircuito

- Preparar o circuito para gravação e realização no kit DE2-115

Diagrama Esquemático

Abra o Quartus II (versão 13.0) e insira o diagrama esquemático do somador completo, conforme a figura abaixo.

Após salvar o arquivo como FullAdder.bdf em uma pasta vazia com nome PROJ2, e crie um projeto FullAdder.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso faça a Análise e Sintese do projeto.

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF) (v 13.0 e 13.1).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome TesteFA.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0)

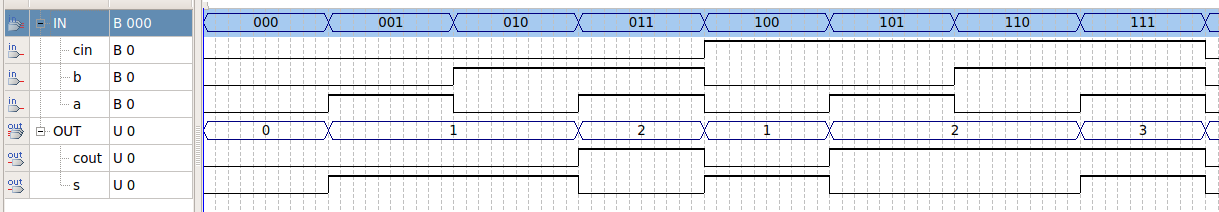

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um somador completo.

- Analise o resultado preenchendo a tabela-verdade abaixo:

| Entradas | Saídas | |||

|---|---|---|---|---|

| cin | a | b | s | cout |

| 0 | 0 | 0 | ||

| 0 | 0 | 1 | ||

| 0 | 1 | 0 | ||

| 0 | 1 | 1 | ||

| 1 | 0 | 0 | ||

| 1 | 0 | 1 | ||

| 1 | 1 | 0 | ||

| 1 | 1 | 1 | ||