Mudanças entre as edições de "Códigos VHDL para uso nas Aulas"

| Linha 139: | Linha 139: | ||

Escreva um código VDHL que implemente a função do decodificador usando uma '''descrição funcional''' do decodificador. | Escreva um código VDHL que implemente a função do decodificador usando uma '''descrição funcional''' do decodificador. | ||

| − | =Multiplexador 2 entradas | + | =Multiplexador 2 entradas e 1 saída= |

{{collapse top|Entidade - entradas e saídas}} | {{collapse top|Entidade - entradas e saídas}} | ||

| Linha 180: | Linha 180: | ||

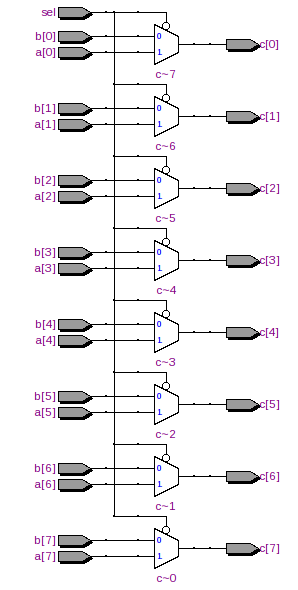

{{collapse top|Circuito RTL desagrupado}} | {{collapse top|Circuito RTL desagrupado}} | ||

[[Arquivo:MUX21_8bitsD.png]] | [[Arquivo:MUX21_8bitsD.png]] | ||

| + | {{collapse bottom}} | ||

| + | |||

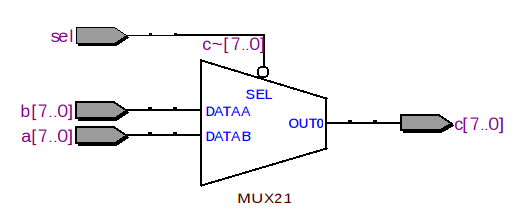

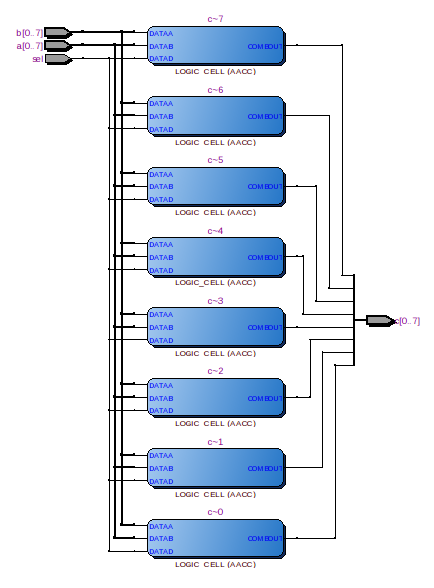

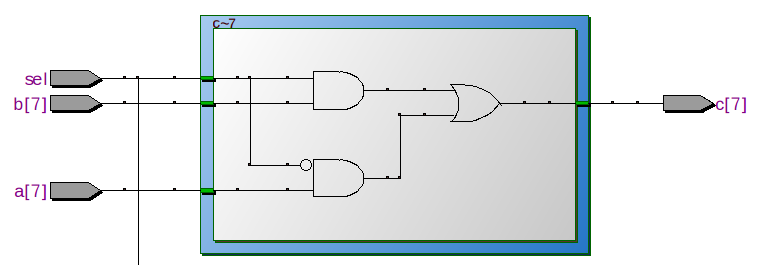

| + | {{collapse top|Tecnology Map}} | ||

| + | [[Arquivo:MUX21_8bitsTM.png]] | ||

| + | [[Arquivo:MUX21_8bitsTMdetalhe.png]] | ||

{{collapse bottom}} | {{collapse bottom}} | ||

Edição das 15h51min de 26 de março de 2012

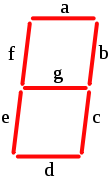

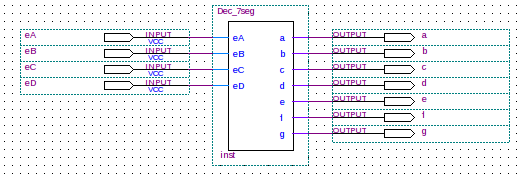

Decodificador de BCD para 7 segmentos

Descrever usando lógica discreta um decodificador de BCD para 7 segmentos. A interface externa do decodificador deve ter as entradas eA, eB, eC e eD, e as saídas os sete segmentos a, b, c, d, e, f, g. Neste exemplo esta sendo considerada a logica negativa onde o segmento acesso corresponde a 0 e apagado -> 1. Entradas só são consideradas válidas de 0 (0000) até 9 (1001), ou seja o circuito não precisa tratar as entradas entre A (1010) e F(1111).

| Código VHDL (lógica discreta) |

|---|

entity Dec_7seg is

port

(

eA,eB,eC,eD : in bit;

a,b,c,d,e,f,g : out bit

);

end Dec_7seg;

architecture discret_logic of Dec_7seg is

begin

--lógica que implementa o segmento a de um display (0,1,2,3,4,5,6,7,8,9), sem minimização.

-- 0 -> aceso (ON), 1 -> apagado (OFF)

a <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND eC AND NOT eB AND NOT eA);

--implemente a lógica dos demais segmentos do display (0,1,2,3,4,5,6,7,8,9), sem minimização.

b <= (NOT eD AND eC AND NOT eB AND eA) OR

(NOT eD AND eC AND eB AND NOT eA);

c <= (NOT eD AND NOT eC AND eB AND eA);

d <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND eC AND NOT eB AND NOT eA) OR

(NOT eD AND eC AND eB AND eA);

e <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND NOT eC AND eB AND eA) OR

(NOT eD AND eC AND NOT eB AND NOT eA) OR

(NOT eD AND eC AND NOT eB AND eA) OR

(NOT eD AND eC AND eB AND eA) OR

( eD AND NOT eC AND NOT eB AND eA);

f <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND NOT eC AND eB AND NOT eA) OR

(NOT eD AND NOT eC AND eB AND eA) OR

(NOT eD AND eC AND eB AND eA);

g <= (NOT eD AND NOT eC AND NOT eB AND NOT eA) OR

(NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND eC AND eB AND eA);

end discret_logic;

|

| Código TCL para teste do Hardware |

|---|

|

Use o código tcl abaixo para testar no ModelSim o circuito RTL gerado no Quartus II.

|

- Atividade complementar

Escreva um código VDHL que implemente a função do decodificador usando uma descrição funcional do decodificador.

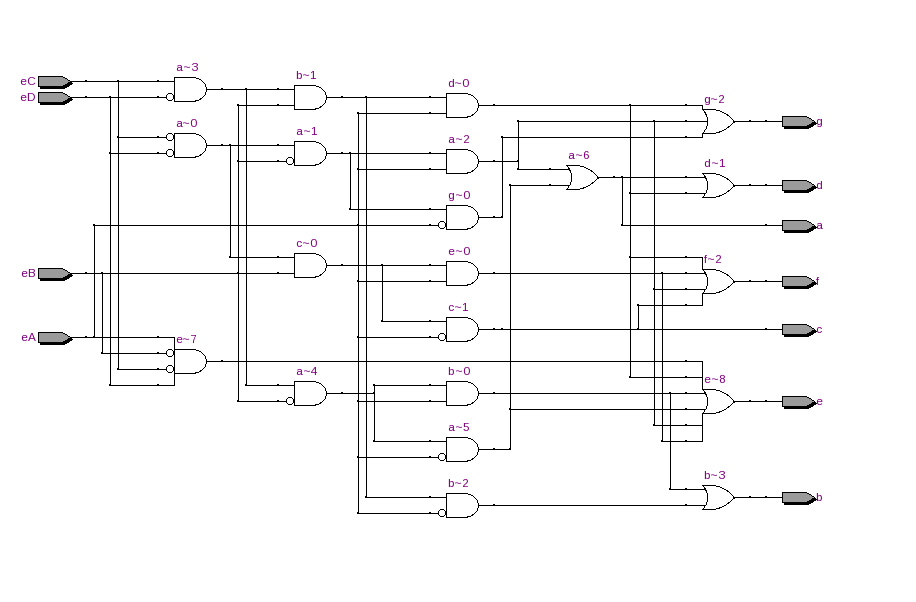

Multiplexador 2 entradas e 1 saída

| Entidade - entradas e saídas |

|---|

|

Complete o código VHDL para que sintetize um multiplexador de 8 bits. ---------------------------------------

LIBRARY ieee;

USE ____;

---------------------------------------

ENTITY ____ IS

PORT (

____ : in STD_LOGIC_VECTOR (7 DOWNTO 0);

____ : in STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____ ;

___ OUT STD_LOGIC_VECTOR ____

);

END ____ ;

---------------------------------------

ARCHITECTURE example OF ____ IS

BEGIN

PROCESS (a, b, ____)

BEGIN

IF (sel = '0') THEN

c <= a;

ELSE

____;

END ____;

END ____;

END ____;

---------------------------------------

|