Mudanças entre as edições de "Oficina NCO e Filtros digitais"

| Linha 150: | Linha 150: | ||

Isso acontece devido à modificação no número de bits do sinal devido às multiplicações realizadas no filtro. Ao abrir a composição do sinal '''filtro''', percebemos que os bits de número 20 a 24 se repetem. Assim, descartamos os bits 21 a 24, mantendo o bit 20 como bit de sinal. Isso é feito na aba '''Setup''' do ''SignalTap II''. Selecione os bits, delete, recompile o projeto, reprograme a placa e capture novamente os sinais. | Isso acontece devido à modificação no número de bits do sinal devido às multiplicações realizadas no filtro. Ao abrir a composição do sinal '''filtro''', percebemos que os bits de número 20 a 24 se repetem. Assim, descartamos os bits 21 a 24, mantendo o bit 20 como bit de sinal. Isso é feito na aba '''Setup''' do ''SignalTap II''. Selecione os bits, delete, recompile o projeto, reprograme a placa e capture novamente os sinais. | ||

| + | |||

| + | [[Imagem:PJI29008-OficinaFiltro4.png|thumb|Composição do sinal de saída do filtro|700px|center]] | ||

| + | <br style="clear:both;"> | ||

Edição das 14h00min de 15 de março de 2017

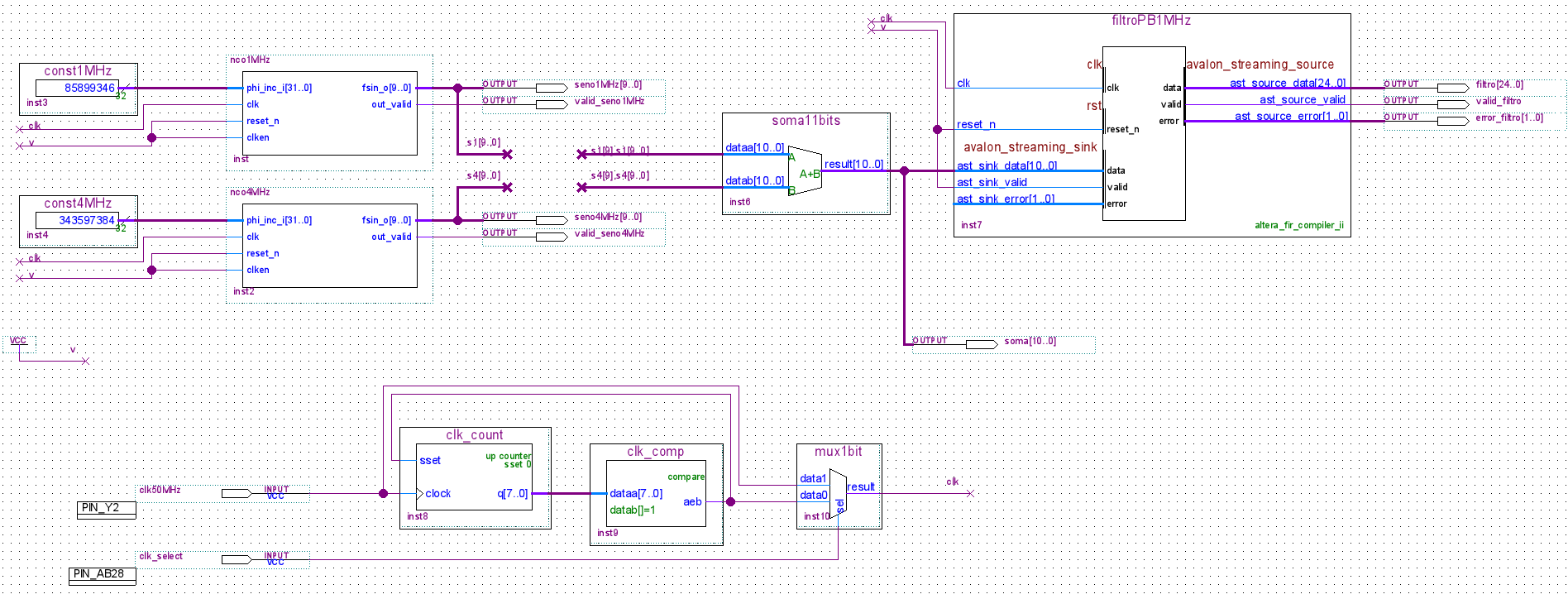

Esta página traz um roteiro para a geração de sinais senoidais e a construção de filtros digitais em FPGAs Altera, usando o Quartus II. O sistema criado (figura abaixo) gera sinais senoidais de 1 MHz e 4 MHz, soma os dois sinais e realiza uma filtragem passa baixas, visando manter apenas o sinal de 1 MHz. Está prevista também a construção de um divisor de clock para realizar uma subamostragem nos sinais. Todos os blocos utilizaram a ferramenta nativa do Quartus II, o MegaWizard Plug-In Manager. O sistema foi desenvolvido no kit didático Altera DE2-115, com um FPGA Cyclone IV EP4CE115F29C7.

- Crie um projeto e adicione um arquivo do tipo Block Diagram/Schematic File

Geração dos sinais senoidais

Nesta seção, dois sinais senoidais serão criados, um de 1 MHz e outro de 4 MHz

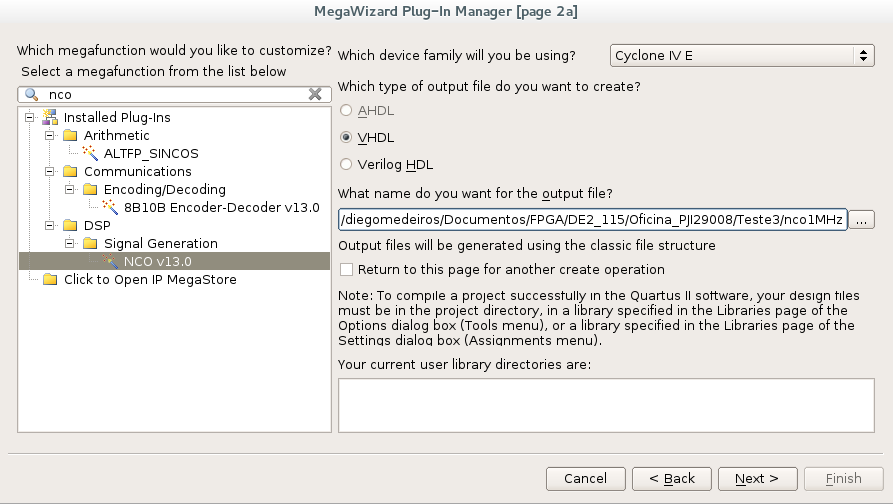

- Abrir o MegaWizard Plug-In Manager (Menu Tools)

- Página 1: Selecionar Create a new custom megafunction variation

- Página 2: Escrever na lupa nco, escolher a pasta para os arquivos e incluir um nome (sugestão: nco1MHz e nco4MHz)

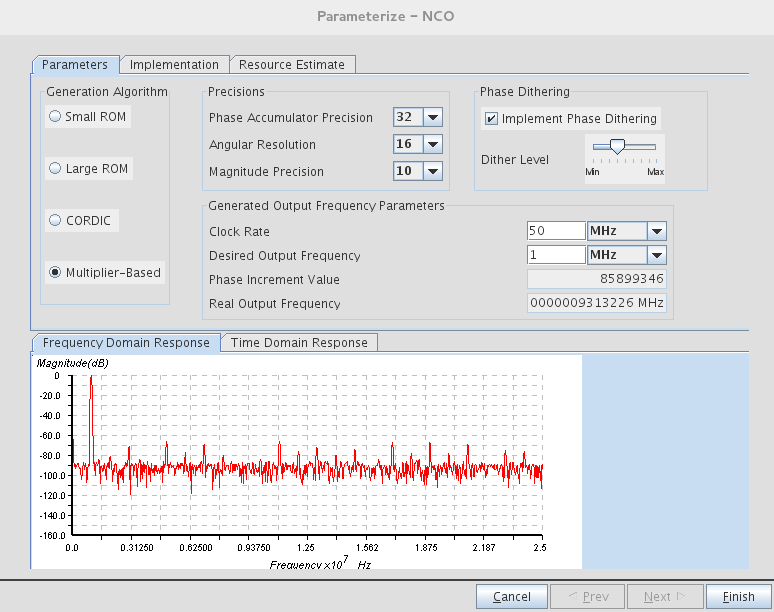

- Na janela do NCO, clique em Step1: Parameterize

- Em Magnitude Precision, escolha o número de bits por amostra desejado para o sinal senoidal (sugestão: 10)

- Em Clock Rate, escolha o clock da placa (no caso, 50 MHz). Digite o valor e tecle ENTER

- Em Desired Output Frequency, escolha a frequência desejada para o sinal senoidal (1 MHz). Digite o valor e tecle ENTER

- Anote o valor disponibilizado em Phase Increment Value (Para 1MHz, 85899346). Você pode dar dois cliques no valor e usar o CTRL+C para copiar. Esse número pode ser encontrado também através da equação:

- onde as siglas se referem às iniciais dos parâmetros

- No canto superior direito da aba Implementation, marque a opção Single Output

- Clique em Finish para encerrar a parametrização

- Clique em Generate para gerar o bloco

- Quando o processamento encerrar, clique em Exit e selecione Yes quando questionado sobre adicionar o arquivo gerado ao projeto

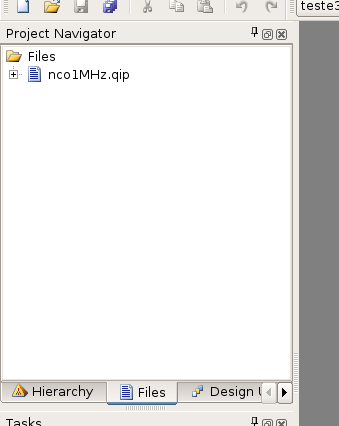

- De volta à janela padrão do Quartus II repare que o arquivo nco1MHz.qip foi adicionado ao projeto

O mesmo procedimento deve ser feito para o NCO de 4 MHz (Phase Increment Value 343597384)

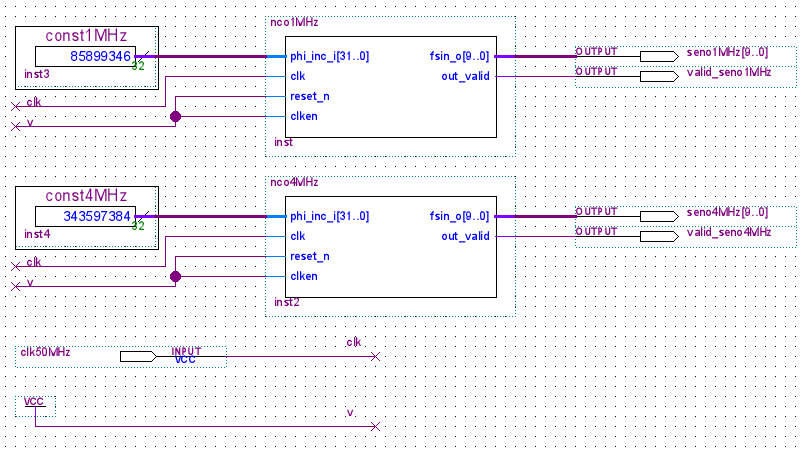

Com os dois NCOs criados, adicione-o ao projeto. Repare que ele possui entradas de clock, um reset ativo baixo (repare no "_n" no nome da entrada), um enable e uma entrada de 32 bits chamada phi_inc_i[31..0]. É através dessa entrada que o NCO é controlado, e a constante Phase Increment Value deve ser passada. Para isso, use um outro MegaWizard, o LPM_CONSTANT. Ao fazer sua configuração, use o nome const1MHz e const4MHz. Sua parametrização é simples, com o número de bits da constante (32, para estar de acordo com o esperado pelo NCO), e o seu valor em decimal (85899346 e 343597384). Na página Summary, marque todos os tipos de arquivo disponíveis.

Adicione os componentes ao projeto e realize as ligações como abaixo:

Compile o projeto, e no Pin Planner (menu Assignments), configure apenas a porta clk50MHz, no Location PIN_Y2

Configurando o SignalTap para visualização dos sinais gerados

- Adicione um arquivo novo ao projeto, e no tipo do arquivo, selecione SignalTap II Logic Analyzer File

- Na aba Setup, dê um duplo-clique na área em branco

- Se ainda não estiver selecionado, clique no botão

para abrir a seção de mais opções

para abrir a seção de mais opções - Em Filter, selecione SignalTap II: pre-synthesis

- Clique no botão List

- Na janela Nodes Found, selecione os sinais (use CTRL):

- seno1MHz

- seno4MHz

- valid_seno1MHz

- valid_seno4MHz

- Jogue para a direita com o botão >

- Clique em OK

- Se ainda não estiver selecionado, clique no botão

- Na janela Signal Configuration, seção Clock, clique no botão ... e use o mesmo procedimento para encontrar o sinal clk50MHz

- Salve o arquivo com o nome stp2.stp

Compile o projeto e faça a programação da placa. Abra o arquivo stp2.stp. Caso necessário, faça a configuração correta da JTAG, podendo usar o botão Scan Chain.

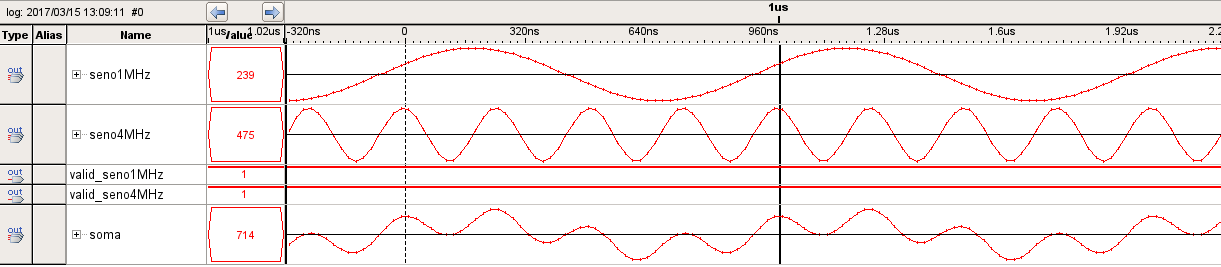

Clicando no botão ![]() , o SignalTap inicia a captação de informações. Os sinais senoidais precisam ainda ser configurados de acordo com o tipo de dado. Pare a captação e clique com o botão direito em cada um, e em Bus Display Format, selecione Signed Line Chart. Na barra superior da ferramenta, clique com o botão direito e escolha Time Units. Digite o valor 50 e selecione MHz no menu. Na mesma barra superior, clique e arraste a barra temporal para fechar um período da onda mais lenta. Repare que ela possui 1 us, equivalente à uma onda de 1 MHz.

, o SignalTap inicia a captação de informações. Os sinais senoidais precisam ainda ser configurados de acordo com o tipo de dado. Pare a captação e clique com o botão direito em cada um, e em Bus Display Format, selecione Signed Line Chart. Na barra superior da ferramenta, clique com o botão direito e escolha Time Units. Digite o valor 50 e selecione MHz no menu. Na mesma barra superior, clique e arraste a barra temporal para fechar um período da onda mais lenta. Repare que ela possui 1 us, equivalente à uma onda de 1 MHz.

Somando os dois sinais

Os sinais senoidais usam bit de sinal obtido via complemento de dois. Para somar os dois sinais, acrescentaremos um bit à representação, e usaremos um MegaWizard para realizar a soma, o LPM_ADD_SUB. Dê ao bloco o nome soma11bits

- Escolha o número de bits dos sinais para 11

- Na aba General 2, mude o tipo da adição para Signed

- Na aba Summary, selecione todos os arquivos disponíveis

Ao adicionar o somador no projeto, puxe uma derivação dos fios de saída de cada sinal senoidal, dando o nome de s1[9..0] e s4[9..0]. Nas portas de entrada do somador, ligue à cada uma das derivações, repetindo bit mais significativo. Para isso, dê os nomes s1[9],s1[9..0] e s4[9],s4[9..0]. Crie uma porta de saída de nome soma[10..0].

Após isso, compile o projeto e adicione a porta soma ao SignalTap II. Compile novamente, faça a programação, e inicie a captura de sinais no SignalTap II. Configure a exibição do sinal de soma da mesma forma que os sinais senoidais.

Criando o filtro no MATLAB

Realizaremos a filtragem do sinal de soma, mantendo apenas o sinal de 1 MHz. Para isso, um filtro passa baixas de frequência de corte de 2,5 MHz será utilizado. Os coeficientes do filtro serão calculados no MATLAB, usando a ferramenta fdatool.

- Abra a ferramenta com o comando fdatool

- No quadro Frequency Specifications, mude a unidade para MHz

- Digite os seguintes valores:

- Fs: 50

- Fpass: 1.5

- Fstop: 3.5

- Clique em Design Filter

- Com o filtro gerado, clique em File -> Export...

- Em Export To, selecione Coefficient File (ASCII)

- Clique em Export, e selecione o local e o nome do arquivo salvo

- Abra o arquivo gerado usando o gedit, e limpe tudo o que não é coeficiente (inclusive linhas em branco)

- Vá no menu e clique em Localizar e substituir...

- Pesquise por "\n" e substitua por ","

- Pesquise por " " e substitua por vazio. Agora o arquivo possui apenas uma linha, com os coeficientes separados por vírgula

- Salve o arquivo com o nome filtroPB.txt

Inserindo o filtro no projeto

De volta ao Quartus II, abra o MegaWizard e procure por FIR, selecionando na lista o FIR Compiler II v13.0. Use o nome filtroPB1MHz.

- Na janela de especificação do filtro, repare na linha File Path, e clique no botão Browse

- Selecione o arquivo filtroPB.txt (caso não apareça opções de navegação pelo sistema de arquivos, digite ou cole o caminho completo para o arquivo)

- Aplique e repare que a curva do filtro se alterou

- Na janela Input/Output Options, altere o Input Bit Width para 11

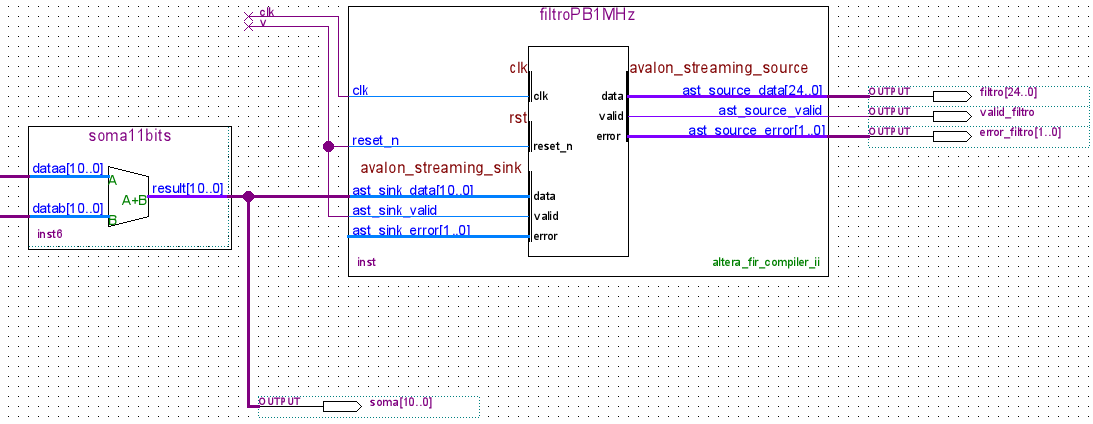

Repare nas opções de saída que o sinal terá 25 bits, mas há opções de truncar ou saturar um número específico dos bits mais significativos e dos bits menos significativos (Configurações Output MSB Rounding, MSB Bits to Remove, Ouput LSD Rounding e LSB Bits to Remove). Por enquanto, estas configurações serão mantidas assim mesmo.

- Na janela de opções de implementação, altere a especificação de frequência de Clock e de amostragem para 50

- Clique em Finish

Depois de adicionar o filtro no projeto, faça as ligações como abaixo:

- Porta clk no sinal clk

- Portas reset_n e ast_sink_valid no sinal v

- Cada porta de saída do bloco numa porta de saída

Depois de compilar, programar e capturar sinais no SignalTap II, repare que a saída do filtro se encontra estranha, como se estivesse atenuada.

Isso acontece devido à modificação no número de bits do sinal devido às multiplicações realizadas no filtro. Ao abrir a composição do sinal filtro, percebemos que os bits de número 20 a 24 se repetem. Assim, descartamos os bits 21 a 24, mantendo o bit 20 como bit de sinal. Isso é feito na aba Setup do SignalTap II. Selecione os bits, delete, recompile o projeto, reprograme a placa e capture novamente os sinais.