Mudanças entre as edições de "DIG222802 AULA12"

(Criou página com '=Laboratório 3= O TERCEIRO experimento da turma de Digital 2 da Engenharia vai ser realizado no LabDIG (Sala 104) entre 14h e 17h45min. Vamos testar um contador/registrador em ...') |

|||

| Linha 1: | Linha 1: | ||

| − | =Laboratório | + | =Laboratório 4 - Simulação Proteus= |

| − | O | + | O quarto Laboratório da turma de Digital 2 da Engenharia vai ser realizado no LabINF (Sala 121) entre às 14h e 17h45min e será dividido em duas partes. Primeiramente, vamos apresentar o software de CAD Eletrônico - Proteus, mostrando área de trabalho, localização de componentes e ligações. E a segunda parte, propor um experimento de simulação de circuitos de memória, utilizando o integrado 7486 e um contador (74193) os dois de quatro bits. A proposta é verificar o funcionamento da memória, como acessar, gravar e ler e exibir o seu conteúdo. |

| + | |||

| + | =Objetivo= | ||

| + | |||

| + | *Apresentar o ambiente de trabalho do proteus e como funciona a ferramenta. | ||

| + | *Testar o funcionamento da memória 7486. | ||

| − | |||

| − | |||

[[Imagem:fig49_DIG222802.png|center|700px]] | [[Imagem:fig49_DIG222802.png|center|700px]] | ||

| Linha 14: | Linha 17: | ||

==Procedimento== | ==Procedimento== | ||

| − | + | #Montar o circuito | |

| − | |||

| − | |||

| − | #Montar o circuito | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

#Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando. | #Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando. | ||

| − | + | ||

==Parte 2== | ==Parte 2== | ||

Edição das 13h56min de 6 de julho de 2016

Laboratório 4 - Simulação Proteus

O quarto Laboratório da turma de Digital 2 da Engenharia vai ser realizado no LabINF (Sala 121) entre às 14h e 17h45min e será dividido em duas partes. Primeiramente, vamos apresentar o software de CAD Eletrônico - Proteus, mostrando área de trabalho, localização de componentes e ligações. E a segunda parte, propor um experimento de simulação de circuitos de memória, utilizando o integrado 7486 e um contador (74193) os dois de quatro bits. A proposta é verificar o funcionamento da memória, como acessar, gravar e ler e exibir o seu conteúdo.

Objetivo

- Apresentar o ambiente de trabalho do proteus e como funciona a ferramenta.

- Testar o funcionamento da memória 7486.

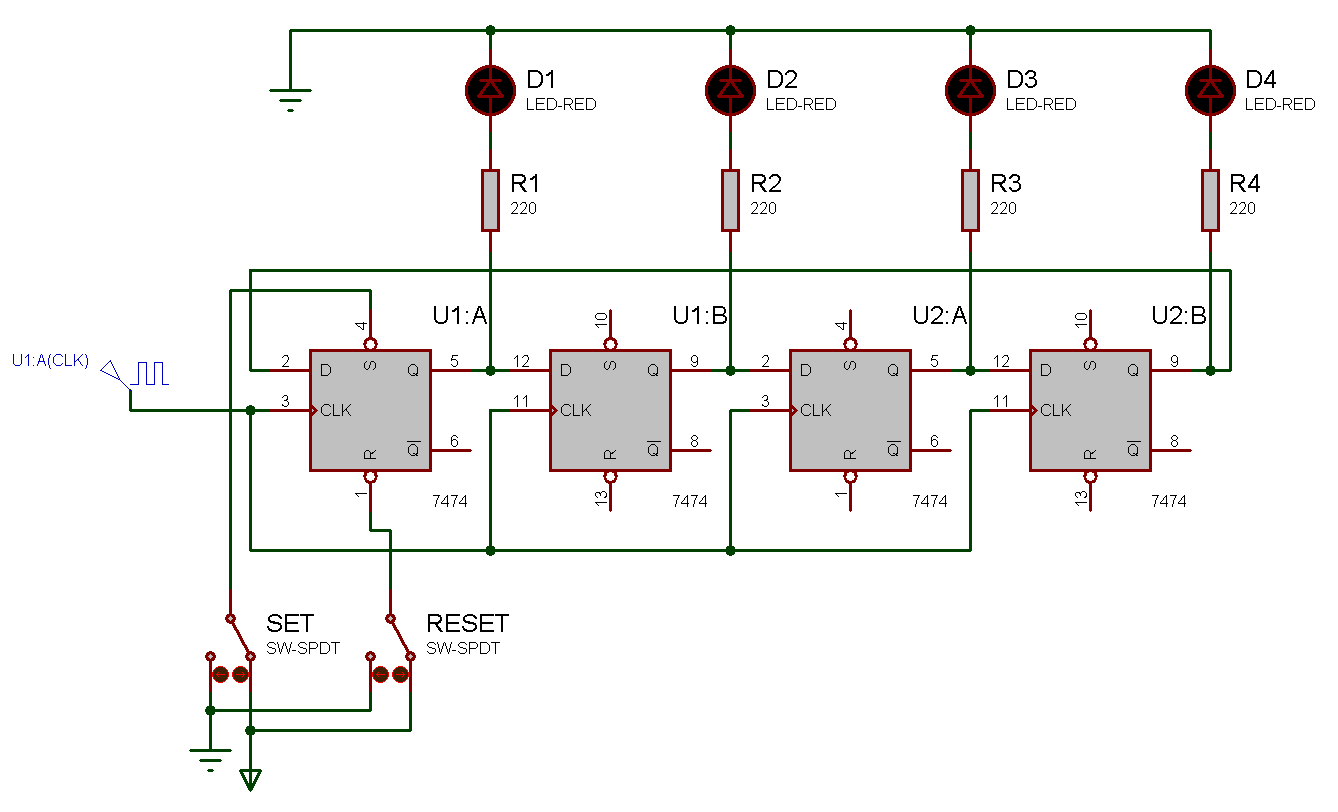

Figura 1 - Registrador em anel de 4 bits.

Procedimento

- Montar o circuito

- Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando.

Parte 2

- Objetivo

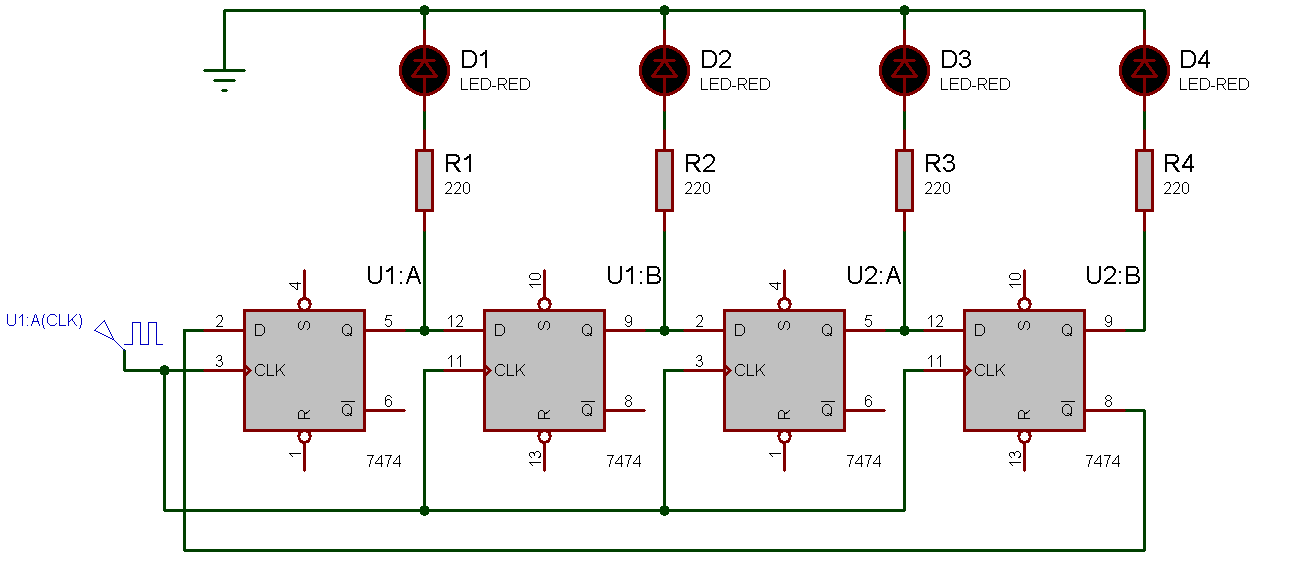

- Alterar o circuito do contador em anel para que ele funcione como contador Jonhson, comprovando seu funcionamento. O circuito é visto da Figura 2.

Figura 2 - Contador Jonhson.

Procedimento

- Mesmas equipes;

- Repetir as ligações utilizando o parte do esquemático dos CIs já realizado;

- Desfazer as ligações do SET e RESET do primeiro FF ligando-os em VCC se necessário;

- Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando.

Parte 3 - Desafio

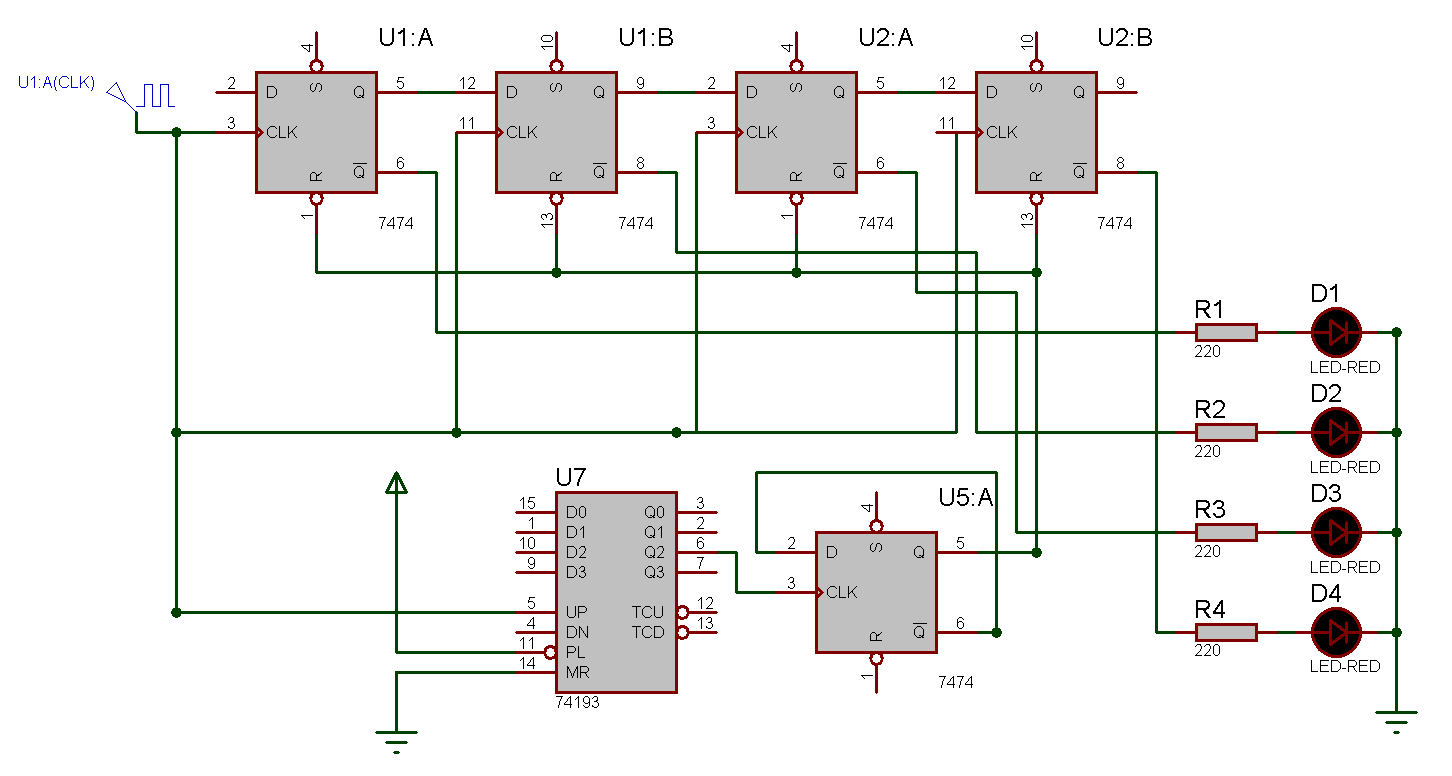

Realizar o circuito do temporizador da sinaleira de quatro estados. A Figura 3 mostra o esquemático do circuito.

Figura 3 - Circuito temporizador da sinaleira de quatro estados.

Material Utilizado

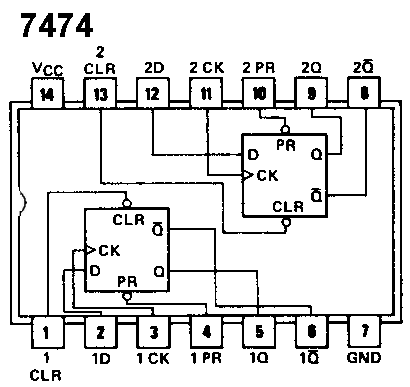

- CI 7474

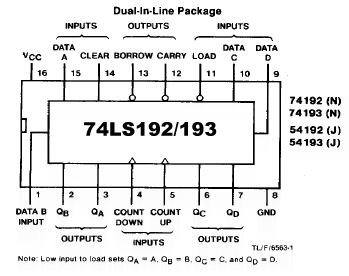

- CI 74193 (contador UP/DOWN 4 bits) (Figura 2)

- fios diversos

- bancada digital

Circuitos

Figura 4 - Esquemático do CI 7474 - Dois FF tipo D.

Figura 5 - Esquemático do CI 74192/74193 - Contador UP/DOWN de 4 bits.

Relatório

O relatório simplificado deverá ser entregue no final da aula. As equipes que não terminaram as duas partes do experimento, mais o desafio, podem fazer o relatório das partes 1 e 2 obrigatoriamente e relatar o que aconteceu com o desafio.

Equipes

- Critérios avaliativos

- Participação: 2

- Montagem: 1

- Administração do tempo: 1

- Escrita (coerente e conclusiva): 6

| << | <> | >> |

|---|