Mudanças entre as edições de "Avaliação 1 - SST"

Ir para navegação

Ir para pesquisar

| (27 revisões intermediárias por 3 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| − | ; | + | <!-- |

| + | ;Avaliação 2 - SST | ||

| + | ;Alunos: Kamila, Leonardo Oliveira e Rogerio. | ||

| + | --> | ||

| + | ==Registrador de deslocamento com data-load== | ||

| − | + | * Um registrador de deslocamento (shift registers - SRs) são circuitos constituidos por um agrupamento de Flip-Flops D em série com a finalidade de armazenar e manipular dados; | |

| − | [[Arquivo:registrador_de_deslocamento_data-load.jpg| | + | * Esse registrador é constituído por vários estágios dependendo do número de Flip-Flops usados, onde a cada variação do clock fará com que um estágio receba o valor do estágio anterior; |

| + | |||

| + | * Um registrador de deslocamento com data load são inseridos multiplexadores apresentando um registrador de deslocamento com capacidade de carregamento (data load) do valor inicial. | ||

| + | |||

| + | [[Arquivo:registrador_de_deslocamento_data-load.jpg|800px|center]] | ||

| + | |||

| + | |||

| + | ;Flip-Flops D | ||

| + | |||

| + | O Flip-Flops D ("data" ou dado, pois armazena o bit de entrada) possui uma entrada, que é ligada diretamente à saída quando o clock é mudado. | ||

| + | |||

| + | [[Arquivo:fflopD.png|200px|center]] | ||

| + | |||

| + | ; Código | ||

| + | :<syntaxhighlight lang=vhdl> | ||

| + | ----- ff_bank (another component) ------ | ||

| + | ENTITY ff_bank IS | ||

| + | GENERIC (bits: POSITIVE); | ||

| + | PORT (d: IN BIT_VECTOR(bits-1 DOWTO 0); | ||

| + | clk: IN BIT; | ||

| + | q: OUT BIT_VECTOR(bits-1 DOWTO 0)); | ||

| + | END ff_bank | ||

| + | |||

| + | ---------------------------------------------------- | ||

| + | |||

| + | ARCHITECTURE ff_bank OF ff_bank IS | ||

| + | BEGIN | ||

| + | PROCESS (clk) | ||

| + | BEGIN | ||

| + | IF (clk'EVENT AND clk='1') THEN | ||

| + | q <= d; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | END ff_bank; | ||

| + | -------------------------------------- | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | |||

| + | O armazenamento de informação no Flip-Flops é feito através das seguintes características no código: | ||

| + | |||

| + | * Sendo o processo sensível apenas à CLK, a informação de entrada será avaliada apenas em casos de alteração nesse sinal. | ||

| + | |||

| + | * A condição CLK = '1' certifica que o corpo da instrução IF será executado apenas na borda de subida do clock (entrada D só terá influência na saída durante a borda de subida do clock). | ||

| + | |||

| + | |||

| + | ;Multiplexador | ||

| + | |||

| + | O Multiplexador é o componente que seleciona uma das duas entrada e coloca na saída. | ||

| + | |||

| + | |||

| + | [[Arquivo:multiplexador.jpg|150px|center]] | ||

| + | |||

| + | ; Código | ||

| + | :<syntaxhighlight lang=vhdl> | ||

| + | entity multiplexer is | ||

| + | |||

| + | generic (bits: positive); | ||

| + | |||

| + | port( | ||

| + | |||

| + | inp1,inp2: in bit_vector(bits-1 downto 0); | ||

| + | sel: in bit; | ||

| + | outp: out bit_vector(bits-1 downto 0)); | ||

| + | |||

| + | end entity; | ||

| + | |||

| + | architecture multi of multiplexer is | ||

| + | begin | ||

| + | |||

| + | outp <= inp1 when sel='0' else inp2; | ||

| + | |||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | A saída do multiplexador depende de qual entrada que esta sendo selecionada: | ||

| + | |||

| + | * A entrada "A" vai estar na saida de "sel=1" | ||

| + | * A entrada "B" vai estar na saida de "sel=0" | ||

| + | |||

| + | |||

| + | |||

| + | ; Código Principal | ||

| + | |||

| + | |||

| + | No código principal são declarados e instanciados os componentes (multiplexadores e flip-flops) do registrador de deslocamento. | ||

| + | |||

| + | |||

| + | ; Código | ||

| + | :<syntaxhighlight lang=vhdl> | ||

| + | use work.my_package.all; | ||

| + | |||

| + | ---shift_register---- | ||

| + | |||

| + | entity shift_register is | ||

| + | |||

| + | generic (m: integer := 4; -- numero de estagios | ||

| + | n: integer := 8); -- numero de bits dos sinais carregados | ||

| + | port( | ||

| + | clk, load: in bit; | ||

| + | x: in x_input(1 to m); | ||

| + | d: in bit_vector(n-1 downto 0); | ||

| + | q: out bit_vector(n-1 downto 0)); | ||

| + | |||

| + | end entity; | ||

| + | |||

| + | architecture structural of shift_register is | ||

| + | |||

| + | signal temp1: x_input(0 to m); | ||

| + | signal temp2: x_input(1 to m); | ||

| + | |||

| + | ----------------------------------------------------- | ||

| + | |||

| + | component multiplexer is | ||

| + | generic (bits: positive); | ||

| + | |||

| + | port( | ||

| + | |||

| + | inp1,inp2: in bit_vector(bits-1 downto 0); | ||

| + | sel: in bit; | ||

| + | outp: out bit_vector(bits-1 downto 0)); | ||

| + | |||

| + | end component; | ||

| + | |||

| + | |||

| + | component ff_bank is | ||

| + | |||

| + | generic (bits: positive); | ||

| + | |||

| + | port( | ||

| + | |||

| + | d: in bit_vector(bits-1 downto 0); | ||

| + | clk: in bit; | ||

| + | q: out bit_vector(bits-1 downto 0)); | ||

| + | |||

| + | end component; | ||

| + | ----------------------------------------------------- | ||

| + | begin | ||

| + | |||

| + | temp1(0) <= d; | ||

| + | g: for i in 1 to m generate | ||

| + | |||

| + | mux: multiplexer generic map(n) | ||

| + | port map (temp1(i-1), x(i), load, temp2(i)); | ||

| + | |||

| + | ff: ff_bank generic map(n) | ||

| + | port map (temp2(i), clk, temp1(i)); | ||

| + | end generate; | ||

| + | |||

| + | q <= temp1(m); | ||

| + | |||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | Através de um laço de repetição são criados os 4 estágio que formam o registrador de deslocamento. | ||

| + | Em cada estagio é instânciado um multiplexador e um flip-flop: | ||

| + | |||

| + | [[Arquivo:estagios.jpg|800px|center]] | ||

| + | |||

| + | ;Funcionamento: | ||

| + | |||

| + | |||

| + | [[Arquivo:registrador_de_deslocamento_data-load.jpg|800px|center]] | ||

| + | |||

| + | |||

| + | * Quando load = '1', o vetor x é carregado no SR na próxima borda ascendente do clock. | ||

| + | * Quando load = '0' o circuito opera como um SR regular. | ||

| + | |||

| + | ; Forma de onda: | ||

| + | [[Arquivo:registrador.jpg|1100px|center]] | ||

==Debouncer para Chave== | ==Debouncer para Chave== | ||

Edição atual tal como às 07h39min de 26 de novembro de 2015

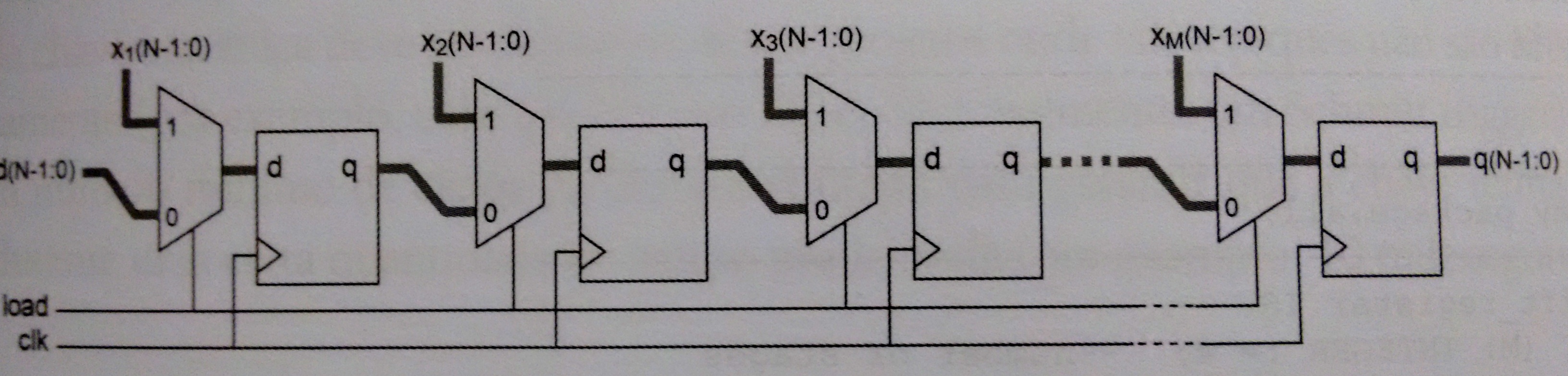

Registrador de deslocamento com data-load

- Um registrador de deslocamento (shift registers - SRs) são circuitos constituidos por um agrupamento de Flip-Flops D em série com a finalidade de armazenar e manipular dados;

- Esse registrador é constituído por vários estágios dependendo do número de Flip-Flops usados, onde a cada variação do clock fará com que um estágio receba o valor do estágio anterior;

- Um registrador de deslocamento com data load são inseridos multiplexadores apresentando um registrador de deslocamento com capacidade de carregamento (data load) do valor inicial.

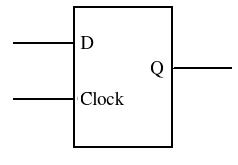

- Flip-Flops D

O Flip-Flops D ("data" ou dado, pois armazena o bit de entrada) possui uma entrada, que é ligada diretamente à saída quando o clock é mudado.

- Código

----- ff_bank (another component) ------ ENTITY ff_bank IS GENERIC (bits: POSITIVE); PORT (d: IN BIT_VECTOR(bits-1 DOWTO 0); clk: IN BIT; q: OUT BIT_VECTOR(bits-1 DOWTO 0)); END ff_bank ---------------------------------------------------- ARCHITECTURE ff_bank OF ff_bank IS BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN q <= d; END IF; END PROCESS; END ff_bank; --------------------------------------

O armazenamento de informação no Flip-Flops é feito através das seguintes características no código:

- Sendo o processo sensível apenas à CLK, a informação de entrada será avaliada apenas em casos de alteração nesse sinal.

- A condição CLK = '1' certifica que o corpo da instrução IF será executado apenas na borda de subida do clock (entrada D só terá influência na saída durante a borda de subida do clock).

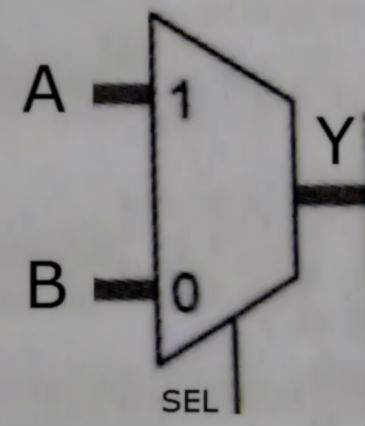

- Multiplexador

O Multiplexador é o componente que seleciona uma das duas entrada e coloca na saída.

- Código

entity multiplexer is generic (bits: positive); port( inp1,inp2: in bit_vector(bits-1 downto 0); sel: in bit; outp: out bit_vector(bits-1 downto 0)); end entity; architecture multi of multiplexer is begin outp <= inp1 when sel='0' else inp2; end architecture;

A saída do multiplexador depende de qual entrada que esta sendo selecionada:

- A entrada "A" vai estar na saida de "sel=1"

- A entrada "B" vai estar na saida de "sel=0"

- Código Principal

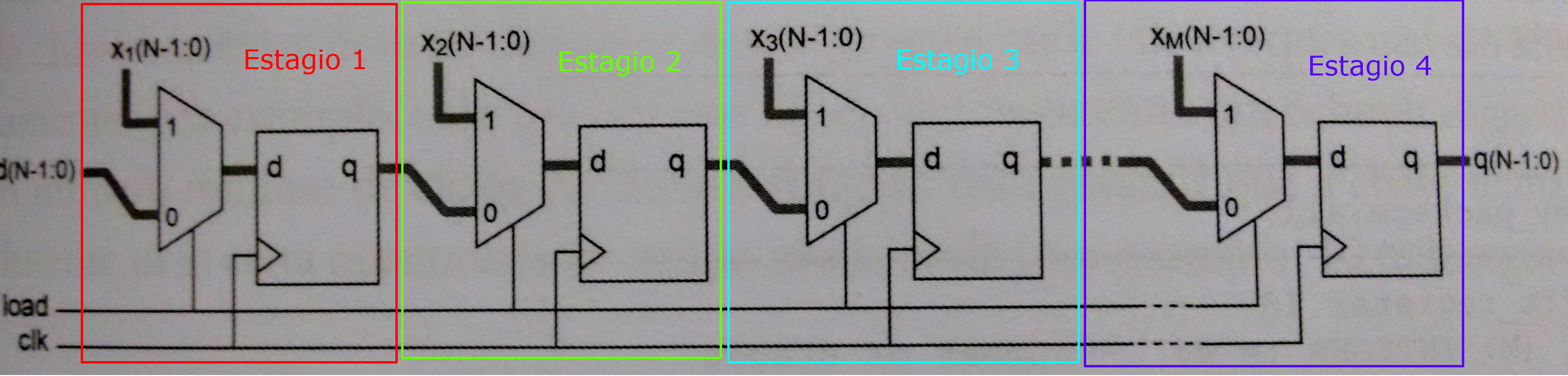

No código principal são declarados e instanciados os componentes (multiplexadores e flip-flops) do registrador de deslocamento.

- Código

use work.my_package.all; ---shift_register---- entity shift_register is generic (m: integer := 4; -- numero de estagios n: integer := 8); -- numero de bits dos sinais carregados port( clk, load: in bit; x: in x_input(1 to m); d: in bit_vector(n-1 downto 0); q: out bit_vector(n-1 downto 0)); end entity; architecture structural of shift_register is signal temp1: x_input(0 to m); signal temp2: x_input(1 to m); ----------------------------------------------------- component multiplexer is generic (bits: positive); port( inp1,inp2: in bit_vector(bits-1 downto 0); sel: in bit; outp: out bit_vector(bits-1 downto 0)); end component; component ff_bank is generic (bits: positive); port( d: in bit_vector(bits-1 downto 0); clk: in bit; q: out bit_vector(bits-1 downto 0)); end component; ----------------------------------------------------- begin temp1(0) <= d; g: for i in 1 to m generate mux: multiplexer generic map(n) port map (temp1(i-1), x(i), load, temp2(i)); ff: ff_bank generic map(n) port map (temp2(i), clk, temp1(i)); end generate; q <= temp1(m); end architecture;

Através de um laço de repetição são criados os 4 estágio que formam o registrador de deslocamento. Em cada estagio é instânciado um multiplexador e um flip-flop:

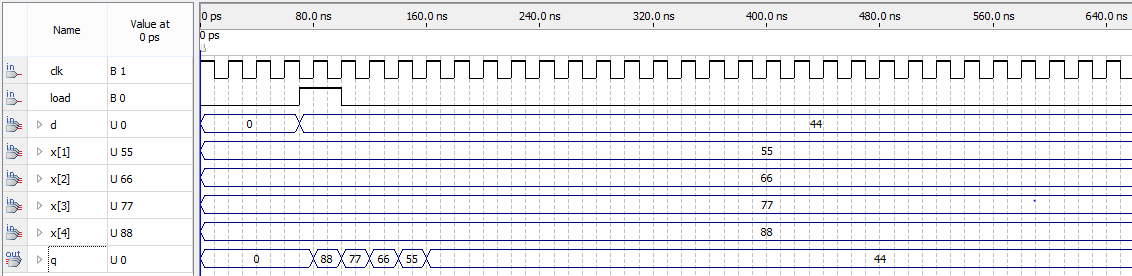

- Funcionamento

- Quando load = '1', o vetor x é carregado no SR na próxima borda ascendente do clock.

- Quando load = '0' o circuito opera como um SR regular.

- Forma de onda

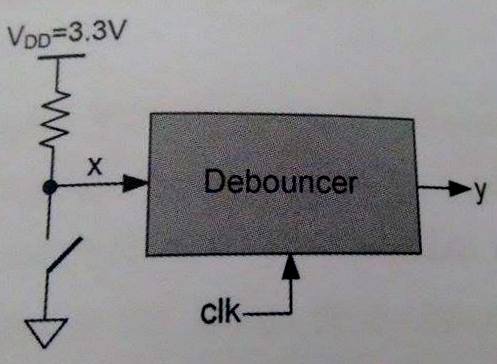

Debouncer para Chave

- FUNCIONAMENTO

- Chave fechada (y='0') : x deve permanecer baixo por no mínimo 10ms sem interrupção.

- Chave aberta (y='1') : x deve permanecer alto por no mínimo 10ms sem interrupção.

- PARÂMETROS

- fclk: inteiro = 1. Define a frequência do clock (kHz);

- twindow: inteiro = 10. Define a janela de tempo (ms);

- x: Valor de entrada (std_logic);

- clk: Valor de clock (std_logic);

- y: Buffer, neste caso variável de saída (std_logic);

- Constant max: Definida por um inteiro resultado da multiplicação das variáveis de entrada [fclk * twindow = (1kHz * 10ms = 10 bordas positivas de clock)].

- Process é sensível a borda de subida do clock;

- Count: Afim de verificar em quantos períodos de clock a entrada x ficou alta/baixa.

- CÓDIGO

library ieee; use ieee.std_logic_1164.all; entity debouncer is generic( fclk: integer := 1; --clock freq in kHz twindow: integer := 10); --time window in ms port( x: in std_logic; clk: in std_logic; y : buffer std_logic); end entity; architecture key of debouncer is constant max: integer := fclk * twindow; begin process(clk) variable count : integer range 0 to max; begin if(clk'event and clk='1') then if(y /= x) then count := count + 1; if(count = max) then y <= x; count := 0; end if; else count := 0; end if; end if; end process; end architecture;

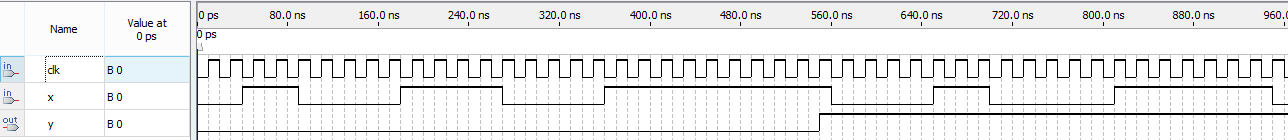

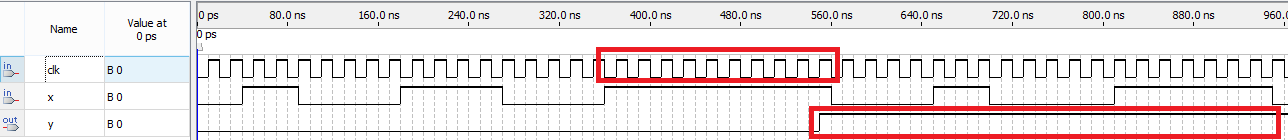

- FORMA DE ONDA