Mudanças entre as edições de "MIC-2014-1-CST Introdução aos Microcoprocessadores"

| (78 revisões intermediárias por 4 usuários não estão sendo mostradas) | |||

| Linha 176: | Linha 176: | ||

*Apresentação do projeto de expansão de memória | *Apresentação do projeto de expansão de memória | ||

*Apresentação do Terceiro Projeto | *Apresentação do Terceiro Projeto | ||

| + | |||

| + | |||

| + | =AULA 8 - Dia 26/3/2014= | ||

=Terceiro Mini-Projeto= | =Terceiro Mini-Projeto= | ||

| Linha 184: | Linha 187: | ||

[http://ecee.colorado.edu/~mcclurel/sn74ls373rev5.pdf Datasheet do 74LS373] | [http://ecee.colorado.edu/~mcclurel/sn74ls373rev5.pdf Datasheet do 74LS373] | ||

| + | |||

| + | =Link para o esqueleto do projeto= | ||

| + | |||

| + | Baixar o arquivo de projeto [http://www.sj.ifsc.edu.br/~eraldo/MIC-2014-1/MemoriaRegistrador.pdsprj] | ||

| + | |||

| + | =Link para tutorial Spice/Proteus= | ||

| + | |||

| + | http://www.youspice.com/ys/gettingstartedwithlabcenterproteus.3sp | ||

| + | |||

| + | =AULA 9 - Dia 27/3/2014= | ||

| + | |||

| + | *Desenvolvimento e apresentação do mini-projeto 3 | ||

| + | |||

| + | ALUNOS QUE DEFENDERAM: GIOVANA, FERNANDA, ALFREDO, EVANDER, VINICISU, RENATO, ANTONIO | ||

| + | |||

| + | =AULA 10 - Dia 2/4/2014= | ||

| + | |||

| + | *DApresentação do Mini-projeto 2 para os alunos que ainda não tinham defendido: Reanto, Fernanda e Evander | ||

| + | |||

| + | =AULA 11 - Dia 3/4/2014= | ||

| + | |||

| + | *Apresentação do Mini-Projeto 4: Implemenatação de uma (parte) de uma Unidade Lógica e Aritmética | ||

| + | |||

| + | ==As partes de um sistema computacional== | ||

| + | |||

| + | Até o presente momento tivemos uma ideia dos seguintes elementos de um sistema computacional: | ||

| + | *Unidade de Entrada (e Saída) | ||

| + | *memória primária | ||

| + | *CPU | ||

| + | *barramentos: dados, endereço e controle | ||

| + | |||

| + | A CPU é dividida em registradores (implementamos o registrador A), a unidade de controle (que tem sido você) e a unidade lógica e aritmética. Neste mini-projeto vamos passar uma ideia do que é esta unidade, implementando um somador de bytes. | ||

| + | |||

| + | ==Mini-projeto 4== | ||

| + | |||

| + | Acrescentar ao mini-projeto 3 um circuito somador de bytes com entrada de C e saída de carry. Armazenar o Carry em um flip flop tipo D (registrador de 1 bit). O somandor será implementado com o 74LS283. Usar uma subsheet para implementar o somador bufferizado com buffer tris-tate 74LS241. | ||

| + | |||

| + | ==Parte 1 - Demonstração de como o 74LS283 funciona usando o Proteus== | ||

| + | |||

| + | [http://www.skot9000.com/ttl/datasheets/283.pdf Data sheet do 74LS283] | ||

| + | |||

| + | [http://www.jameco.com/Jameco/Products/ProdDS/47167.pdf Data sheet do 74LS241] | ||

| + | |||

| + | ==Parte 2 - Construção do circuito em sub-sheet== | ||

| + | |||

| + | O seguinte sistema foi implementado: | ||

| + | |||

| + | [http://www.sj.ifsc.edu.br/~eraldo/MIC-2014-1/testeSomador.pdsprj Somador] | ||

| + | |||

| + | [http://www.sj.ifsc.edu.br/~eraldo/MIC-2014-1/MemoriaRegistradoresSomador.pdsprj MemoriaRegistrador] | ||

| + | |||

| + | =AULA 12 - Dia 9/4/2014= | ||

| + | |||

| + | ==Parte 3 - Inclusão do circuito no mini-projeto 3== | ||

| + | |||

| + | ==Parte 4 - Desenvolvimento do sistema completo== | ||

| + | |||

| + | |||

| + | =AULA 13 - Dia 16/04/2014= | ||

| + | |||

| + | Arquivo parcial de projeto [http://www.sj.ifsc.edu.br/~eraldo/MIC-2014-1/MemoriaRegistradoresSomador.pdsprj] | ||

| + | |||

| + | =AULA 14 - Dia 23/04/2014= | ||

| + | |||

| + | ==Objetivos== | ||

| + | |||

| + | *Apresentar o princípio de funcionamento de um sistema microprocessado | ||

| + | |||

| + | ==Material== | ||

| + | |||

| + | [http://www.sj.ifsc.edu.br/~eraldo/MIC-2014-1/IntroducaoMic-parte2.pdf Aula de Introdução] | ||

| + | |||

| + | =AULA 15 - Dia 24/04/2014= | ||

| + | |||

| + | Continuação: Princípio de funcionamento de um istema microprocessado. | ||

| + | |||

| + | =AULA 16 - Dia 30/04/2014= | ||

| + | |||

| + | ==Objetivos== | ||

| + | |||

| + | *apresentação do miniprojeto 3 | ||

| + | *apresentação do miniprojeto 4 | ||

| + | |||

| + | ==Miniprojeto 4== | ||

| + | |||

| + | Implementar um circuito lógico combinacional usando o microntrolador 8051. Função lógica a ser implementada: | ||

| + | |||

| + | Fernanda: | ||

| + | <math>Y = AB + CD + \overline{D}E</math> | ||

| + | Renato: | ||

| + | <math>Y = \overline{A} + BCD + \overline{D}EF</math> | ||

| + | Evander: | ||

| + | <math>Y = A\overline{B} + CD + \overline{D}E\overline{F}</math> | ||

| + | Antônio: | ||

| + | <math>Y = ABCD + \overline{D}EF</math> | ||

| + | Alfredo: | ||

| + | <math>Y = AB\overline{CD} + \overline{D}EF</math> | ||

| + | Giovana: | ||

| + | <math>Y = \overline{AB}CD + \overline{D}EF</math> | ||

| + | Vinícius: | ||

| + | <math>Y = \overline{ABC}D + \overline{DE}F</math> | ||

| + | |||

| + | ==Fundamentação== | ||

| + | |||

| + | *Criação de um projeto simples, no Proteus, usando o 80C31, 2 chaves LOGICSTATES e um PROBESTATE associados | ||

| + | a pinos da porta P1. | ||

| + | *Criação de um programa PORTA E; | ||

| + | *Mostrar a memória de programa, memória de BITS, as portas e o CARRY | ||

| + | *Explorar as instruções de movimentação de bit, operações lógicas de bit e JMP incondicional; | ||

| + | *Explorar execução passo a passo, breakpoint etc. | ||

| + | |||

| + | [[arquivo:OperacoesBit.pdf| Nota Operações com bit]] | ||

| + | |||

| + | =AULA - Dia 8/05/2014= | ||

| + | |||

| + | =AULA - Dia 9/05/2014= | ||

| + | |||

| + | =AULA - Dia 14/05/2014= | ||

| + | |||

| + | Defesa do Mini Projeto 5 | ||

| + | |||

| + | Giovana - B | ||

| + | |||

| + | Antônio - D | ||

| + | |||

| + | Renato - B | ||

| + | |||

| + | Alfredo - B | ||

| + | |||

| + | Fernanda - C | ||

| + | |||

| + | Evander - B | ||

| + | |||

| + | Vinícius - B | ||

| + | |||

| + | =AULA - Dia 15/05/2014= | ||

| + | |||

| + | ==Objetivos== | ||

| + | |||

| + | *Avaliação final do Mini-Projeto 4 | ||

| + | *Apresentação do Mini-Projeto 5 | ||

| + | |||

| + | ==MiniProjeto 6== | ||

| + | |||

| + | ===Objetivo=== | ||

| + | |||

| + | Este projeto tem por objetivo trabalhar a operação com bits utilizando instruções de jump condicional e | ||

| + | o acesso a memória de bits. A definição de pinos com EQU será apresentada. | ||

| + | |||

| + | ====Exemplo 1==== | ||

| + | |||

| + | <code> | ||

| + | ;==================================================================== | ||

| + | ; RESET and INTERRUPT VECTORS | ||

| + | ;==================================================================== | ||

| + | |||

| + | ; Reset Vector | ||

| + | org 0000h | ||

| + | jmp Start | ||

| + | |||

| + | ;==================================================================== | ||

| + | ; CODE SEGMENT | ||

| + | ;==================================================================== | ||

| + | |||

| + | org 0100h | ||

| + | Start: | ||

| + | ; Write your code here | ||

| + | jb P1.0, alarme_on | ||

| + | clr P2.0 | ||

| + | clr 00h | ||

| + | jmp pto2 | ||

| + | alarme_on: | ||

| + | setb P2.0 | ||

| + | setb 00h | ||

| + | pto2: | ||

| + | jmp Start | ||

| + | Loop: | ||

| + | jmp Loop | ||

| + | |||

| + | ;==================================================================== | ||

| + | END | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ===Referencias=== | ||

| + | |||

| + | [http://courses.cs.washington.edu/courses/cse466/01au/Lab/A251.pdf Manual do Assembly] | ||

| + | [http://www.win.tue.nl/~aeb/comp/8051/set8051.html Lista de Instruções] | ||

| + | |||

| + | ====Exemplo 2 - Usando EQU ==== | ||

| + | |||

| + | <code> | ||

| + | ;==================================================================== | ||

| + | ; DEFINITIONS | ||

| + | ;==================================================================== | ||

| + | CH_ON_OFF EQU P1.0 | ||

| + | LED_ON_OFF EQU P2.0 | ||

| + | |||

| + | |||

| + | ;==================================================================== | ||

| + | ; VARIABLES | ||

| + | ;==================================================================== | ||

| + | |||

| + | STATUS_ON_OFF EQU 00h | ||

| + | |||

| + | ;==================================================================== | ||

| + | ; RESET and INTERRUPT VECTORS | ||

| + | ;==================================================================== | ||

| + | |||

| + | ; Reset Vector | ||

| + | org 0000h | ||

| + | jmp Start | ||

| + | |||

| + | ;==================================================================== | ||

| + | ; CODE SEGMENT | ||

| + | ;==================================================================== | ||

| + | |||

| + | org 0100h | ||

| + | Start: | ||

| + | ; Write your code here | ||

| + | jb CH_ON_OFF , alarme_on | ||

| + | clr LED_ON_OFF | ||

| + | clr STATUS_ON_OFF | ||

| + | jmp pto2 | ||

| + | alarme_on: | ||

| + | setb LED_ON_OFF | ||

| + | setb STATUS_ON_OFF | ||

| + | pto2: | ||

| + | jmp Start | ||

| + | Loop: | ||

| + | jmp Loop | ||

| + | |||

| + | ;==================================================================== | ||

| + | END | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ===O Projeto=== | ||

| + | |||

| + | Desenvolver um alarme com 4 entradas digitais (sensores). O sensor está desligado com o estado 0. Se pelo menos um sensor for desligado um alarme deve ser disparado. O alarme é uma saída digital que alterna o estado quando ativada. Se desativada permanece em 0. O alarme deve ter um uma saída indicando se está em operação ou não. Uma entrada adicional habilita o funcionamento do alarme (pode ser usada para desligar o alarme). Para maior flexibilidade, cada sensor pode ser desabilitado individualmente através de uma entrada digital associada a ele. Quando um sensor for violado uma saída digital deve indicar seu estado através do estado 1. Tão logo todos os sensores estejam desabilitados o alarme deixa de disparar. | ||

| + | |||

| + | ===Parte 1 - Mapeamento de Entradas e Saídas === | ||

| + | |||

| + | |||

| + | |||

| + | ===Parte 2 - Fluxograma=== | ||

| + | |||

| + | =AULA - Dia 21/05/2014= | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | Desenvolver o miniprojeto 5 | ||

| + | |||

| + | =AULA - Dia 28/05/2014= | ||

| + | |||

| + | GREVE ÔNIBUS = Somente Fernda compareceu | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | Desenvolver o miniprojeto 5 | ||

| + | |||

| + | |||

| + | |||

| + | =Acesso por bits= | ||

| + | |||

| + | =Proposta de Esqueleto do MiniProjeto 5= | ||

| + | |||

| + | |||

| + | <code> | ||

| + | ; Created: qui mai 22 2014 | ||

| + | ; Processor: 80C31 | ||

| + | ; Compiler: ASEM-51 (Proteus) | ||

| + | ;==================================================================== | ||

| + | |||

| + | $NOMOD51 | ||

| + | $INCLUDE (8051.MCU) | ||

| + | |||

| + | ;==================================================================== | ||

| + | ; DEFINITIONS | ||

| + | ;==================================================================== | ||

| + | |||

| + | SS1 EQU P1.0 | ||

| + | SS2 EQU P1.1 | ||

| + | SS3 EQU P1.2 | ||

| + | SS4 EQU P1.3 | ||

| + | STATUS_ALARME EQU 00h | ||

| + | |||

| + | SAIDA_ALARME EQU P2.0 | ||

| + | |||

| + | |||

| + | |||

| + | ;==================================================================== | ||

| + | ; VARIABLES | ||

| + | ;==================================================================== | ||

| + | |||

| + | |||

| + | ;==================================================================== | ||

| + | ; RESET and INTERRUPT VECTORS | ||

| + | ;==================================================================== | ||

| + | |||

| + | ; Reset Vector | ||

| + | org 0000h | ||

| + | jmp Start | ||

| + | |||

| + | ;==================================================================== | ||

| + | ; CODE SEGMENT | ||

| + | ;==================================================================== | ||

| + | |||

| + | org 0100h | ||

| + | Start: | ||

| + | ; Write your code here | ||

| + | clr STATUS_ALARME | ||

| + | jb SS1, trata_sensor1 | ||

| + | pt_s2: | ||

| + | jb SS2, trata_sensor2 | ||

| + | pt_s3: | ||

| + | jb SS3, trata_sensor3 | ||

| + | pt_s4: | ||

| + | jb SS4, trata_sensor4 | ||

| + | |||

| + | trata_status: | ||

| + | jb STATUS_ALARME, trata_disparo | ||

| + | clr SAIDA_ALARME | ||

| + | jmp Start | ||

| + | trata_disparo: | ||

| + | cpl SAIDA_ALARME | ||

| + | jmp Start | ||

| + | |||

| + | trata_sensor1: | ||

| + | setb STATUS_ALARME | ||

| + | jmp pt_s2 | ||

| + | trata_sensor2: | ||

| + | setb STATUS_ALARME | ||

| + | jmp pt_s3 | ||

| + | trata_sensor3: | ||

| + | setb STATUS_ALARME | ||

| + | jmp pt_s4 | ||

| + | trata_sensor4: | ||

| + | setb STATUS_ALARME | ||

| + | jmp trata_status | ||

| + | |||

| + | Loop: | ||

| + | jmp Loop | ||

| + | |||

| + | ;==================================================================== | ||

| + | END | ||

| + | |||

| + | </syntaxhighlight> | ||

| + | |||

| + | http://www.win.tue.nl/~aeb/comp/8051/set8051.html | ||

| + | |||

| + | http://courses.cs.washington.edu/courses/cse466/01au/Lab/A251.pdf | ||

| + | |||

| + | =AULA - Dia 29/05/2014= | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | *discutir a memória do 8051 | ||

| + | *apresentar o conceito de subprograma: instruções lcall e ret | ||

| + | *apresentar a instrução [http://www.keil.com/support/man/docs/is51/is51_djnz.htm DJNZ] direto: | ||

| + | |||

| + | |||

| + | =AULA - Dia 4/06/2014 = | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | *Avaliar o miniprojeto 5 | ||

| + | *Apresentar o miniprojeto 6 | ||

| + | |||

| + | ==Conttinução da fundamentação teórica== | ||

| + | |||

| + | [[arquivo:ControleFluxo.pdf| Controle de Fluxo/Pilha e Subrotinas]] | ||

| + | |||

| + | ==Miniprojeto 7== | ||

| + | |||

| + | *Acrescentar ao miniprojeto 6 as seguintes funções: | ||

| + | **O alarme deverá tocar (piscar) 100 vezes; | ||

| + | **Cada sensor e o disparo de alarme deverá ser tratado como subrotina (usar lcall -ret) | ||

| + | **Ao ser habilitado o alarme deverá esperar 1 minuto antes de entrar em operação. | ||

| + | |||

| + | ==Material de Apoio== | ||

| + | |||

| + | =AULA - Dia 11/06/2014 = | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | *Modos de Endereçamento no 8051 | ||

| + | *uso de instrução cjne para elaborar loops | ||

| + | |||

| + | ==Material de Apoio== | ||

| + | |||

| + | |||

| + | [[Media:Aula8-ModosEndereçamento-Exercícios.pdf]] | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ==Exercício 1== | ||

| + | |||

| + | Iniciar um bloco de memória RAM interna de 50h até 7fh com o valor E5h. | ||

| + | |||

| + | Solução: | ||

| + | |||

| + | <code> | ||

| + | . | ||

| + | mov A,#0E5h | ||

| + | mov R0,#50h | ||

| + | inicio: | ||

| + | mov @R0,A | ||

| + | inc R0 | ||

| + | cjne R0,#80h,inicio | ||

| + | |||

| + | loop: jmp loop | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | =AULA - Dia 12/06/2014 = | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | *Avaliar Mini-projeto 7 | ||

| + | *Começar Mini-Projeto 8: explorar a memória RAM interna, endereçamentos direto, indireto, imediato e por registrador. | ||

| + | |||

| + | ==Mini-Projeto 6== | ||

| + | |||

| + | O diagrama em blocos para o mini-projeto 6 é apresentado a seguir: | ||

| + | |||

| + | [[imagem:MIC2014-Eraldo-Mini-Projeto6.jpg|center|410px]] | ||

| + | |||

| + | O objetivo do projeto é construir um programa que permite entrar e visualizar | ||

| + | dados da RAM interna desde 00F até FFH. As seguintes funcionalidades | ||

| + | devem ser previstas: | ||

| + | #Escrever dados em uma posição da RAM: O usuário entra com o endereço e com os dados, aciona o sinal de escrita (leva a 0) e habilita a operação (RET); | ||

| + | #Ler dados: O usuário entra com o endereço a ser lido, aciona o sinal de leitura e habilita o sistema. | ||

| + | #Escrever dados crescente: O usuário coloca um dado, habilita dados crescente e habilita o sistema (RET). O dado é escrito na posição 0 da Ram Interna e a partir deste endereço o programa escreve sequencialmente na memória (até FF) o dado incrementado de 1. Exemplo: Suponha que o dado foi 10. Na posição da memória 0 será escrito 10, na posição 1 será escrito 11 etc. Quando estourar em 255 o sistema começa em 0. | ||

| + | #Escrever dados decrescente: similar ao anterior mas decrescente. | ||

| + | |||

| + | Observações: | ||

| + | |||

| + | (1) Colocar displays hexadecimais para visualizar os dados/endereços de entrada e saída. | ||

| + | |||

| + | (2) No caso de duas ou mais funcionalidades serem ativadas simultaneamente o sistema deve apresentar um "E" piscando no display de saída de dados. | ||

| + | |||

| + | =AULA - Dia 18/06/2014 = | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | *Avaliar miniprojeto 6 | ||

| + | *Continuar desenvolvimento mini-projeto 7 | ||

| + | |||

| + | |||

| + | =AULA - Dia 25/06/2014 = | ||

| + | |||

| + | ==Objetivo== | ||

| + | |||

| + | *Avaliar o miniprojeto 9 | ||

| + | *Apresentar o Miniprojeto 8 envolvendo operações aritméticas e lógicas | ||

| + | |||

| + | ==Descrição do Miniprojeto 8== | ||

| + | |||

| + | Acrescentar ao miniprojeto 7 três funconalidades adicionais: | ||

| + | *Operação de soma com dois operandos na memória RAM interna. Os dois endereços são fornecidos pelos barramentos de entrada e ao selecionar a opção de soma é mostrado na saída a soma dos operandos. | ||

| + | *Operação de and lógico byte a byte com dois operandos da memória RAM interna; | ||

| + | |||

| + | |||

| + | OBS: mostrar o estado do FLAG CARRY | ||

| + | |||

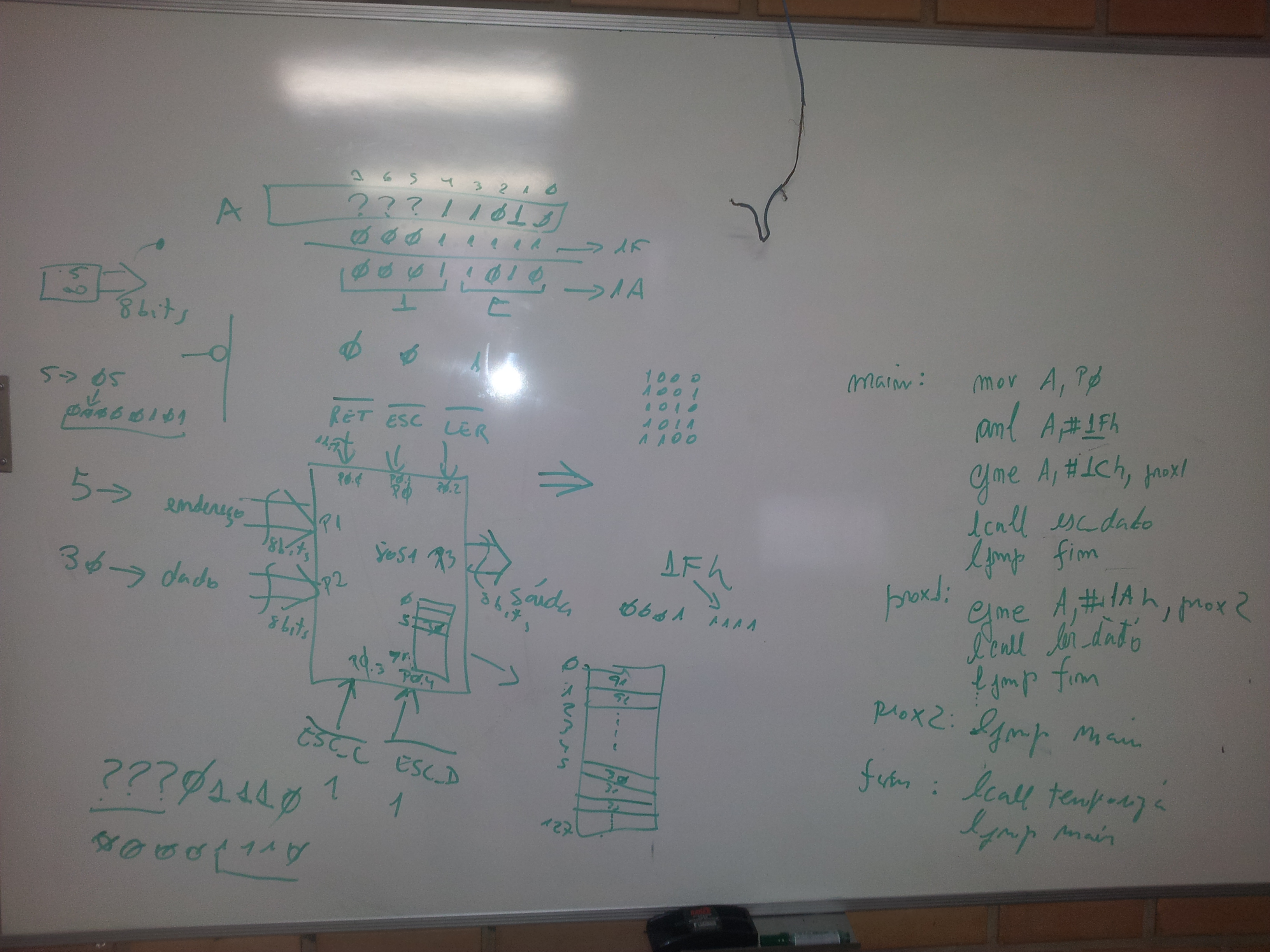

| + | ==Rascunho do Quadro== | ||

| + | |||

| + | [[imagem:MIC2014-Eraldo-Quadro25-06-2014.jpg|center|410px]] | ||

| + | |||

| + | ==Referências== | ||

| + | |||

| + | [[Arquivo:MIC-OperacoesArimeticas.pdf| Operações Aritméticas e Lógicas]] | ||

| + | |||

| + | |||

| + | =AULA - Dia 25/06/2014 = | ||

| + | |||

| + | ==Exemplo do Professor== | ||

| + | |||

| + | |||

| + | [[imagem:MIC2014-Eraldo-MiniProjeto6.jpg|center|410px]] | ||

| + | |||

| + | =AULA - Dia 2/07/2014 = | ||

| + | |||

| + | ==Avaliação do Miniprojeto 7== | ||

| + | |||

| + | ==Início do Miniprojeto 8== | ||

| + | |||

| + | =AULA DIA 3/7/2014= | ||

| + | |||

| + | ==Projeto de Recuperação== | ||

| + | |||

| + | Implementar um dispositivo capaz de interagir com um usuário no sentido de receber dados na sua memória RAM interna entre 60H e 7FH e apresentar a soma aritmética, a operação AND, OR e XORL de todos os bytes da RAM entre dois endereços fornecidos pelo usuário. A soma aritmética deve ser um número de 13 bits, portanto, a saida deve usar 8 bits de uma porta mais 5 bits de outra porta. | ||

| + | |||

| + | =AULA DIA 9/7/2014= | ||

| + | |||

| + | *Desenho ilustrativo do projeto de recuperação | ||

| + | |||

| + | [[imagem:MIC2014-Eraldo-Rec.jpg|center|410px]] | ||

Edição atual tal como às 22h47min de 14 de julho de 2014

DADOS GERAIS DA DISCIPLINA

- Professor: Eraldo Silveira e Silva (email: eraldo@ifsc.edu.br)

- Link da Ementa: Ementa

Avaliação

- 12 miniprojetos - 1 conceito por projeto - desprezado 2 conceitos para fins de avaliação

- recuperação - 1 avaliação escrita geral sobre a disciplina

PLANEJAMENTO 2014-1

| Aula | Data | Horas | Conteúdo | Recursos | |

|---|---|---|---|---|---|

| 1 | 12/2 | 2 | Introdução a disciplina. Avaliação. | Laboratório | |

| 2 | 13/2 | 2 | Conceitos associados a memórias. Barramento de dados, endereços e controle. | Laboratório | |

| 3 | 19/2 | 2 | Apresentação do Proteus. Apresentação do Mini-projeto 1 – acesso manual a uma memória de RAM de 2K | Laboratório | |

| 4 | 20/2 | 2 | Desenvolvimento do Mini-projeto 1 | Laboratório | |

| 5 | 26/2 | 2 | Avaliação do Mini-projeto 1 | Laboratório | |

| 6 | 27/2 | 2 | Defesa de TCC2 | Laboratório | |

| 7 | 6/3 | 2 | Apresentação do Mini-Projeto 2 – Expansão de memória RAM de 2K para 8K | Laboratório | |

| 8 | 12/3 | 2 | Desenvolvimento do Mini-projeto 2 | Laboratório | |

| 9 | 13/3 | 2 | Avaliação do Mini-projeto 2 | Laboratório | |

| 10 | 20/3 | 2 | Apresentação do Mini-projeto 3 – Movimentação manual de dados entre memórias e registradores | Laboratório | |

| 11 | 26/3 | 2 | Desenvolvimento do Mini-projeto 3 | Laboratório | |

| 12 | 27/3 | 2 | Avaliação do Mini-projeto 3 | Laboratório | |

| 13 | 2/4 | 2 | Apresentação do Mini-projeto 4 – Operação manual de soma entre dados armazenados na memória | Laboratório | |

| 14 | 3/4 | 2 | Desenvolvimento do Mini-projeto 4 | Laboratório | |

| 15 | 9/4 | 2 | Avaliação do Mini-projeto 4 | Laboratório | |

| 16 | 10/4 | 2 | Apresentação do Mini-projeto 5 – Introdução ao microcontrolador: movimentando dados da memória externa com o microcontrolador. | Laboratório | |

| 17 | 16/4 | 2 | Desenvolvimento do Mini-projeto 5 | Laboratório | |

| 18 | 17/4 | 2 | Avaliação do Mini-projeto 5 | Laboratório | |

| 19 | 23/4 | 2 | Apresentação do Mini-projeto 6 – Movimentação da memória interna (modos de endereçamento) | Laboratório | |

| 20 | 24/4 | 2 | Desenvolvimento do Mini-projeto 6 | Laboratório | |

| 21 | 30/4 | 2 | Avaliação do Mini-projeto 6 | Laboratório | |

| 22 | 7/5 | 2 | Apresentação do Mini-Projeto 7 – Subrotinnas e Stack | Laboratório | |

| 23 | 8/5 | 2 | Desenvolvimento do mini-projeto 7 | Laboratório | |

| 24 | 14/5 | 2 | Avaliação do Mini-Projeto 7 - | Laboratório | |

| 25 | 15/5 | 2 | Apresentação do Mini-Projeto 8 – Operação com aritméticas e lógicas | Laboratório | |

| 26 | 21/5 | 2 | Desenvolvimento do mini-projeto 8 | Laboratório | |

| 27 | 22/5 | 2 | Avaliação do Mini-Projeto 8 | Laboratório | |

| 28 | 28/5 | 2 | Apresentação do Mini-Projeto 9 – Operação com bits | Laboratório | |

| 29 | 29/5 | 2 | Desenvolvimento do mini-projeto 9 | Laboratório | |

| 30 | 4/6 | 2 | Avaliação do Mini-Projeto 9 | Laboratório | |

| 31 | 5/6 | 2 | Apresentação do Mini-Projeto 10 – Acesso a portas I | Laboratório | |

| 32 | 11/6 | 2 | Avaliação do Mini-Projeto 10 | Laboratório | |

| 33 | 12/6 | 2 | Desenvolvimento do mini-projeto 10 | Laboratório | |

| 34 | 18/6 | 2 | Apresentação do Mini-Projeto 11 – Temprizadores e contadores | Laboratório | |

| 35 | 25/6 | 2 | Desenvolvimento do mini-projeto 11 | Laboratório | |

| 36 | 26/6 | 2 | Avaliação do Mini-Projeto 11 | Laboratório | |

| 37 | 2/7 | 2 | Apresentação do Mini-Projeto 12 – Interrupções | Laboratório | |

| 38 | 3/7 | 2 | Desenvolvimento do mini-projeto 12 | Laboratório | |

| 39 | 9/7 | 2 | Avaliação do Mini-Projeto 12 | Laboratório | |

| 40 | 10/7 | 2 | Recuperação Final | Laboratório | |

| TOTAL | 80 | ||||

Aula 1- Dia 12/2/2014

Objetivos

- Apresentação Ementa

- Revisão de alguns conceitos em digital

- Introdução a memórias

- trabalhar memórias na forma de diagrama em blocos

- apresentar barramentos de endereço/dados/controle

- diferenciar conteúdo de endereço de memória;

- apresentar o procedimento de acesso para escrita e para a leitura;

- apresentar um diagrama de tempo simplificado de acesso a memória;

- apresentar a CPU/microcontrolador como a "entidade" que acessa a memória

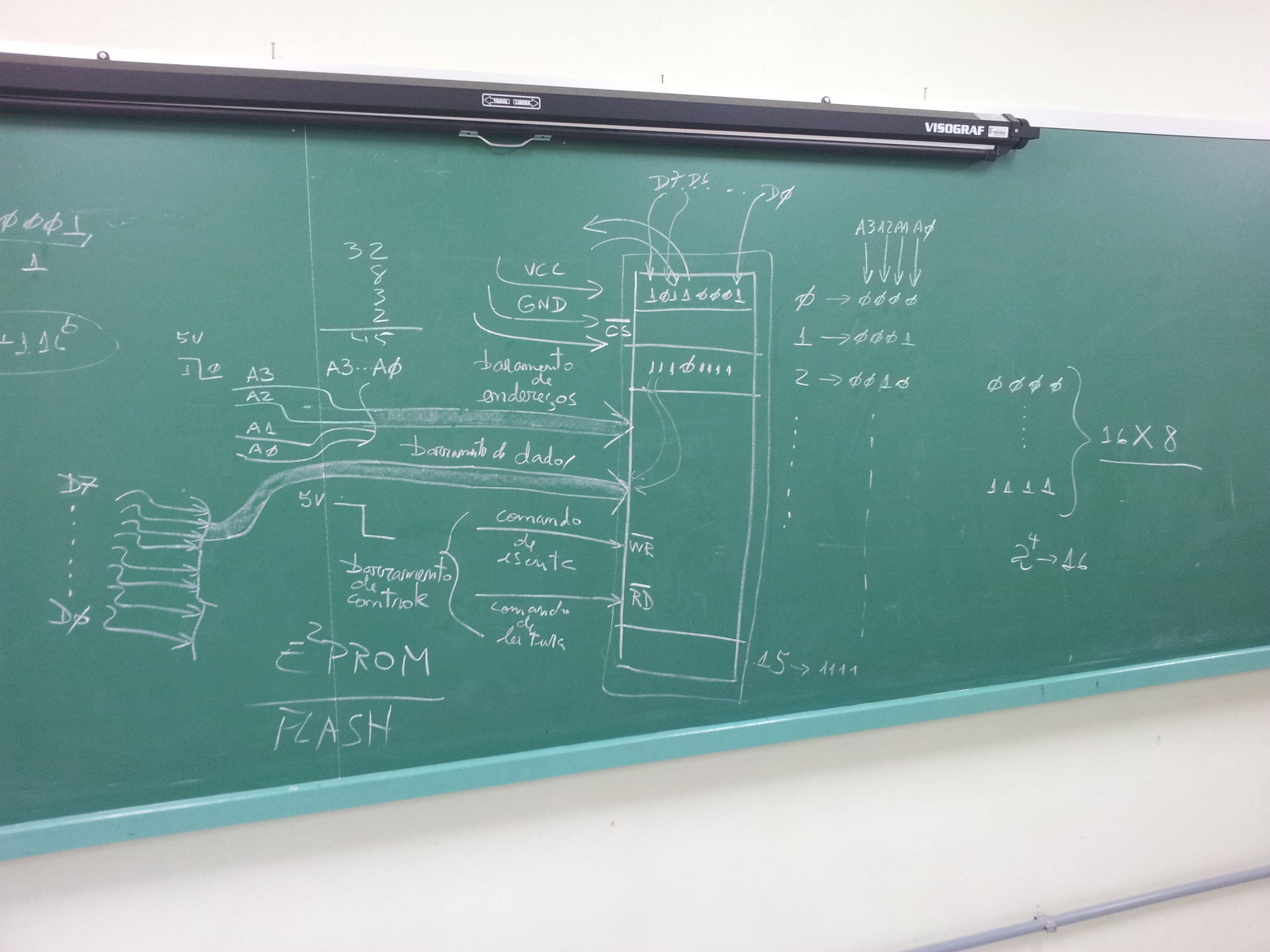

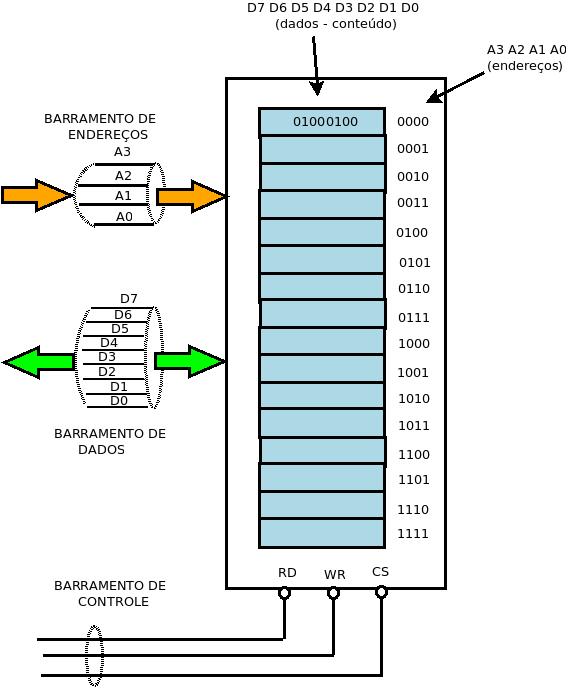

Diagrama em blocos da memória e barramentos

No diagrama abaixo está representado um bloco de memória primária de 16x8 (dezesseis endereços por 8 bits).

- Note que uma posição de memória pode ser vista como uma caixa que possue um endereço e um conteúdo.

- O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits.

ou

Para que us dispositivo externo possa "acessar" a memória para leitura ou escrita, ele deve se utilizar de um conjunto de fios que chamamos de barramentos.

Barramento de Endereços

Este barramento permite determinar o endereço de uma posição a ser acessada na memória. Um barramento de 4 linhas de endereço é designado por A3,A2,A1 e A0.

Supondo uma memória com endereços designados da forma hexadecimal de 0h a Fh. Supondo que A3 seja associado ao bit mais significativo e A0 ao bit menos significativo. Então, para acessar a posição Bh de memória, deve-se injetar A3=1, A2=0, A1=1 e A0=1. Note que

O termo "injetar" significa aqui que um dispositivo externo deve forçar tensão nas linhas do barramento. Esta tensão depende da tecnologia utilizada. Poderia ser, por exemplo, 5V para o nível lógico 1 e 0V par ao nível lógico 0.,

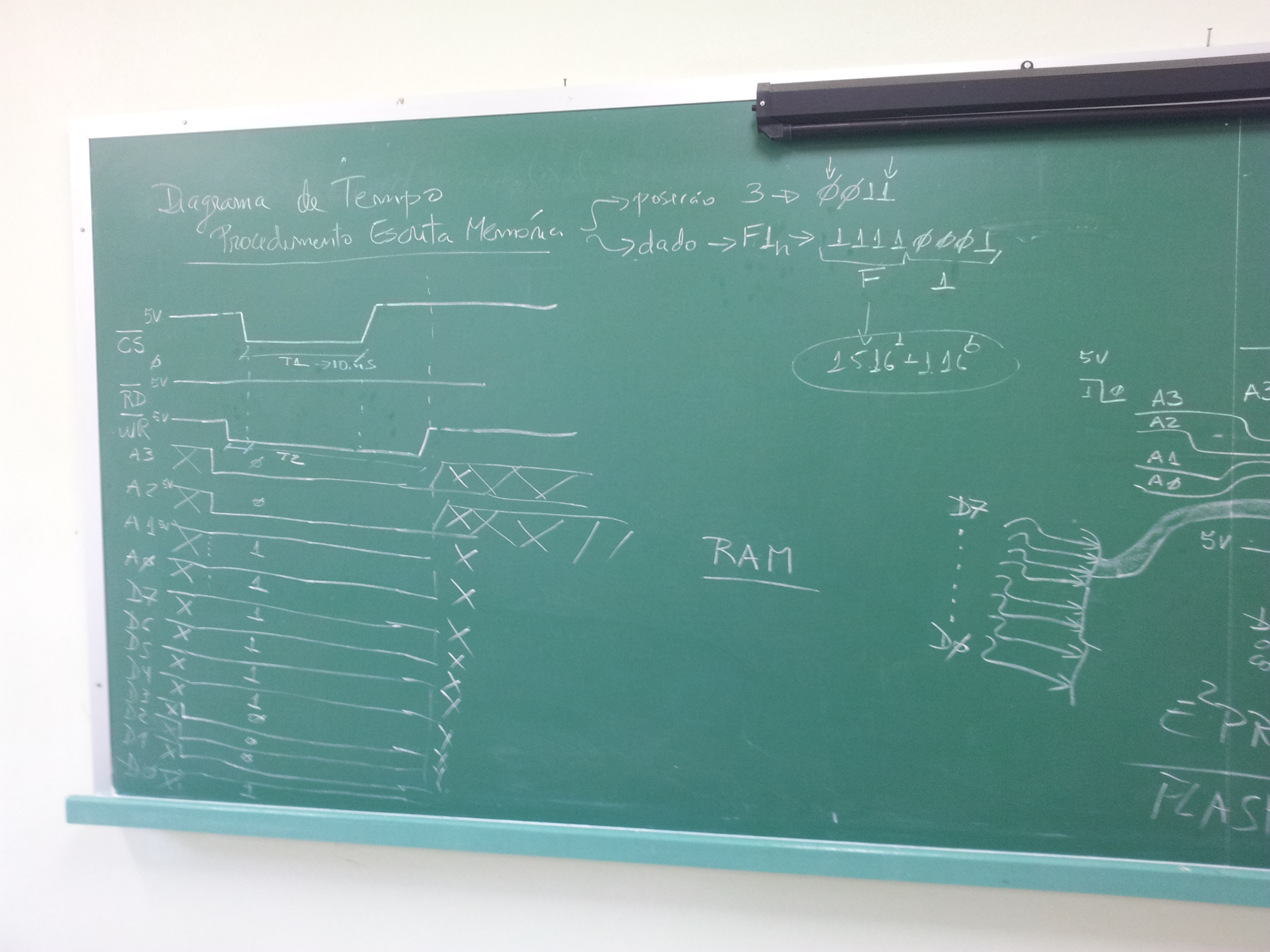

Diagrama de Tempo - Acesso para escrita

Aula 2- Dia 13/2/2014

- continuação da aula anterior.

Aula 3- Dia 19/2/2014

- Objetivos

- Consolidar o conhecimento sobre memórias e barramentos de endereços, dados e controle através de um experimento no Proteus

Experimento 1 - Acesso a memória RAM de 2K x 8 bits

Roteiro:

1.Entrar no Windows.

2.Baixar o arquivo de projeto Experimento 1 MIC. Coloque em um diretório conhecido.

3.Clique sobre o arquivo. O PROTEUS será executado e o projeto aberto.

4.Observe que o projeto está parcialmente pronto. Você pode entrar em modo simulação. O sistema está preparado para que se possa inserir ou ler manualmente posições de memória. Tente colocar o dado AFh na posição 0 de memória e 8Eh na posição 15.

5.Note o Chip Select está habilitado sempre. Coloque uma chave adicional para colocar o Chip Select e repita a operação de gravação anterior.

Exercícios adicionais (Projeto 1)

1.Colocar uma chave de controle do Chip Select (CE). 2.Colocar o seu nome ("Maria da Silva") na memória implmentada no projeto, a partir da posição 0 (endereço). Olhar tabela ASCII. 3.Reimplementar o item dois para gravar nos últimos endereços de memória dos 2K disponíveis.

Aula 4- Dia 26/2/2014

Objetivos

- AValiação do Projeto 1:

ALUNOS OK TAREFA 1: Evander, Vinicius, Renato, Alfredo, Antonio ALUNOS devendo: fernanda

Aula 5 - Dia 6/3/2014

Objetivos

- Apresentar o Mini-Projeto 2 - Expansão de memória

- Fundamentação teórica

- Encaminhamentos

Mini-Projeto 2 - Expansão de Memória

Usando como referência o projeto anterior expandir o sistema de memória de 2Kx8bits para 8Kx8bits. Use o decodificador 74LS139. Para controle das chaves a chave lógica

Fundamentação Teórica

Decodificadores

Usando decodificadores para exppandir sistemas de memória

AULA 5 - Dia 12/3/2014

AULA 6 - Dia 13/3/2014

Desenvolvimento do projeto de expansão de memória.

AULA 7 - Dia 20/3/2014

- Apresentação do projeto de expansão de memória

- Apresentação do Terceiro Projeto

AULA 8 - Dia 26/3/2014

Terceiro Mini-Projeto

Implementar um circuito com 1 memória de 2Kx8 (6116) e um latch 373. Este deverá servir como acumulador em operações para movimentação de memória. Ao final do projeto será solicitado que o aluno entre com dados mnualamente na memória e deloque dados de uma posição para outra na memória. Criar comando WRA (write no acumulador) e RDA (read no acumulador) específicos par o LATCH, de forma a evitar o endereçamento do registrador.

O funcionamento do LATCH 373

Link para o esqueleto do projeto

Baixar o arquivo de projeto [1]

Link para tutorial Spice/Proteus

http://www.youspice.com/ys/gettingstartedwithlabcenterproteus.3sp

AULA 9 - Dia 27/3/2014

- Desenvolvimento e apresentação do mini-projeto 3

ALUNOS QUE DEFENDERAM: GIOVANA, FERNANDA, ALFREDO, EVANDER, VINICISU, RENATO, ANTONIO

AULA 10 - Dia 2/4/2014

- DApresentação do Mini-projeto 2 para os alunos que ainda não tinham defendido: Reanto, Fernanda e Evander

AULA 11 - Dia 3/4/2014

- Apresentação do Mini-Projeto 4: Implemenatação de uma (parte) de uma Unidade Lógica e Aritmética

As partes de um sistema computacional

Até o presente momento tivemos uma ideia dos seguintes elementos de um sistema computacional:

- Unidade de Entrada (e Saída)

- memória primária

- CPU

- barramentos: dados, endereço e controle

A CPU é dividida em registradores (implementamos o registrador A), a unidade de controle (que tem sido você) e a unidade lógica e aritmética. Neste mini-projeto vamos passar uma ideia do que é esta unidade, implementando um somador de bytes.

Mini-projeto 4

Acrescentar ao mini-projeto 3 um circuito somador de bytes com entrada de C e saída de carry. Armazenar o Carry em um flip flop tipo D (registrador de 1 bit). O somandor será implementado com o 74LS283. Usar uma subsheet para implementar o somador bufferizado com buffer tris-tate 74LS241.

Parte 1 - Demonstração de como o 74LS283 funciona usando o Proteus

Parte 2 - Construção do circuito em sub-sheet

O seguinte sistema foi implementado:

AULA 12 - Dia 9/4/2014

Parte 3 - Inclusão do circuito no mini-projeto 3

Parte 4 - Desenvolvimento do sistema completo

AULA 13 - Dia 16/04/2014

Arquivo parcial de projeto [2]

AULA 14 - Dia 23/04/2014

Objetivos

- Apresentar o princípio de funcionamento de um sistema microprocessado

Material

AULA 15 - Dia 24/04/2014

Continuação: Princípio de funcionamento de um istema microprocessado.

AULA 16 - Dia 30/04/2014

Objetivos

- apresentação do miniprojeto 3

- apresentação do miniprojeto 4

Miniprojeto 4

Implementar um circuito lógico combinacional usando o microntrolador 8051. Função lógica a ser implementada:

Fernanda:

Renato:

Evander:

Antônio:

Alfredo:

Giovana:

Vinícius:

Fundamentação

- Criação de um projeto simples, no Proteus, usando o 80C31, 2 chaves LOGICSTATES e um PROBESTATE associados

a pinos da porta P1.

- Criação de um programa PORTA E;

- Mostrar a memória de programa, memória de BITS, as portas e o CARRY

- Explorar as instruções de movimentação de bit, operações lógicas de bit e JMP incondicional;

- Explorar execução passo a passo, breakpoint etc.

AULA - Dia 8/05/2014

AULA - Dia 9/05/2014

AULA - Dia 14/05/2014

Defesa do Mini Projeto 5

Giovana - B

Antônio - D

Renato - B

Alfredo - B

Fernanda - C

Evander - B

Vinícius - B

AULA - Dia 15/05/2014

Objetivos

- Avaliação final do Mini-Projeto 4

- Apresentação do Mini-Projeto 5

MiniProjeto 6

Objetivo

Este projeto tem por objetivo trabalhar a operação com bits utilizando instruções de jump condicional e o acesso a memória de bits. A definição de pinos com EQU será apresentada.

Exemplo 1

- ====================================================================

- RESET and INTERRUPT VECTORS

- ====================================================================

; Reset Vector

org 0000h

jmp Start

- ====================================================================

- CODE SEGMENT

- ====================================================================

org 0100h

Start:

; Write your code here

jb P1.0, alarme_on

clr P2.0

clr 00h

jmp pto2

alarme_on:

setb P2.0

setb 00h

pto2:

jmp Start

Loop:

jmp Loop

- ====================================================================

END

</syntaxhighlight>

Referencias

Exemplo 2 - Usando EQU

- ====================================================================

- DEFINITIONS

- ====================================================================

CH_ON_OFF EQU P1.0

LED_ON_OFF EQU P2.0

- ====================================================================

- VARIABLES

- ====================================================================

STATUS_ON_OFF EQU 00h

- ====================================================================

- RESET and INTERRUPT VECTORS

- ====================================================================

; Reset Vector

org 0000h

jmp Start

- ====================================================================

- CODE SEGMENT

- ====================================================================

org 0100h

Start:

; Write your code here

jb CH_ON_OFF , alarme_on

clr LED_ON_OFF

clr STATUS_ON_OFF

jmp pto2

alarme_on:

setb LED_ON_OFF

setb STATUS_ON_OFF

pto2:

jmp Start

Loop:

jmp Loop

- ====================================================================

END

</syntaxhighlight>

O Projeto

Desenvolver um alarme com 4 entradas digitais (sensores). O sensor está desligado com o estado 0. Se pelo menos um sensor for desligado um alarme deve ser disparado. O alarme é uma saída digital que alterna o estado quando ativada. Se desativada permanece em 0. O alarme deve ter um uma saída indicando se está em operação ou não. Uma entrada adicional habilita o funcionamento do alarme (pode ser usada para desligar o alarme). Para maior flexibilidade, cada sensor pode ser desabilitado individualmente através de uma entrada digital associada a ele. Quando um sensor for violado uma saída digital deve indicar seu estado através do estado 1. Tão logo todos os sensores estejam desabilitados o alarme deixa de disparar.

Parte 1 - Mapeamento de Entradas e Saídas

Parte 2 - Fluxograma

AULA - Dia 21/05/2014

Objetivo

Desenvolver o miniprojeto 5

AULA - Dia 28/05/2014

GREVE ÔNIBUS = Somente Fernda compareceu

Objetivo

Desenvolver o miniprojeto 5

Acesso por bits

Proposta de Esqueleto do MiniProjeto 5

- Created

- qui mai 22 2014

- Processor

- 80C31

- Compiler

- ASEM-51 (Proteus)

- ====================================================================

$NOMOD51

$INCLUDE (8051.MCU)

- ====================================================================

- DEFINITIONS

- ====================================================================

SS1 EQU P1.0

SS2 EQU P1.1

SS3 EQU P1.2

SS4 EQU P1.3

STATUS_ALARME EQU 00h

SAIDA_ALARME EQU P2.0

- ====================================================================

- VARIABLES

- ====================================================================

- ====================================================================

- RESET and INTERRUPT VECTORS

- ====================================================================

; Reset Vector

org 0000h

jmp Start

- ====================================================================

- CODE SEGMENT

- ====================================================================

org 0100h

Start:

; Write your code here

clr STATUS_ALARME

jb SS1, trata_sensor1

pt_s2:

jb SS2, trata_sensor2

pt_s3:

jb SS3, trata_sensor3

pt_s4:

jb SS4, trata_sensor4

trata_status:

jb STATUS_ALARME, trata_disparo

clr SAIDA_ALARME

jmp Start

trata_disparo:

cpl SAIDA_ALARME

jmp Start

trata_sensor1:

setb STATUS_ALARME

jmp pt_s2

trata_sensor2:

setb STATUS_ALARME

jmp pt_s3

trata_sensor3:

setb STATUS_ALARME

jmp pt_s4

trata_sensor4:

setb STATUS_ALARME

jmp trata_status

Loop:

jmp Loop

- ====================================================================

END

</syntaxhighlight>

http://www.win.tue.nl/~aeb/comp/8051/set8051.html

http://courses.cs.washington.edu/courses/cse466/01au/Lab/A251.pdf

AULA - Dia 29/05/2014

Objetivo

- discutir a memória do 8051

- apresentar o conceito de subprograma: instruções lcall e ret

- apresentar a instrução DJNZ direto:

AULA - Dia 4/06/2014

Objetivo

- Avaliar o miniprojeto 5

- Apresentar o miniprojeto 6

Conttinução da fundamentação teórica

Miniprojeto 7

- Acrescentar ao miniprojeto 6 as seguintes funções:

- O alarme deverá tocar (piscar) 100 vezes;

- Cada sensor e o disparo de alarme deverá ser tratado como subrotina (usar lcall -ret)

- Ao ser habilitado o alarme deverá esperar 1 minuto antes de entrar em operação.

Material de Apoio

AULA - Dia 11/06/2014

Objetivo

- Modos de Endereçamento no 8051

- uso de instrução cjne para elaborar loops

Material de Apoio

Media:Aula8-ModosEndereçamento-Exercícios.pdf

Exercício 1

Iniciar um bloco de memória RAM interna de 50h até 7fh com o valor E5h.

Solução:

.

mov A,#0E5h

mov R0,#50h

inicio:

mov @R0,A

inc R0

cjne R0,#80h,inicio

loop: jmp loop

</syntaxhighlight>

AULA - Dia 12/06/2014

Objetivo

- Avaliar Mini-projeto 7

- Começar Mini-Projeto 8: explorar a memória RAM interna, endereçamentos direto, indireto, imediato e por registrador.

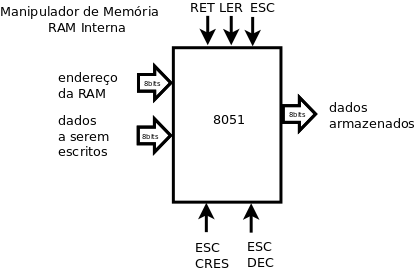

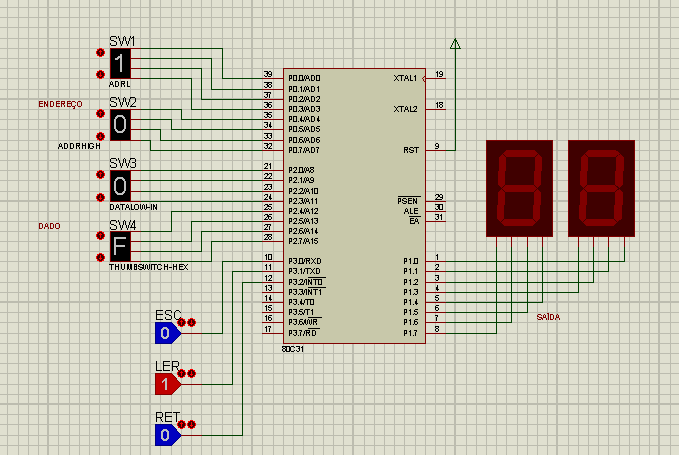

Mini-Projeto 6

O diagrama em blocos para o mini-projeto 6 é apresentado a seguir:

O objetivo do projeto é construir um programa que permite entrar e visualizar

dados da RAM interna desde 00F até FFH. As seguintes funcionalidades

devem ser previstas:

- Escrever dados em uma posição da RAM: O usuário entra com o endereço e com os dados, aciona o sinal de escrita (leva a 0) e habilita a operação (RET);

- Ler dados: O usuário entra com o endereço a ser lido, aciona o sinal de leitura e habilita o sistema.

- Escrever dados crescente: O usuário coloca um dado, habilita dados crescente e habilita o sistema (RET). O dado é escrito na posição 0 da Ram Interna e a partir deste endereço o programa escreve sequencialmente na memória (até FF) o dado incrementado de 1. Exemplo: Suponha que o dado foi 10. Na posição da memória 0 será escrito 10, na posição 1 será escrito 11 etc. Quando estourar em 255 o sistema começa em 0.

- Escrever dados decrescente: similar ao anterior mas decrescente.

Observações:

(1) Colocar displays hexadecimais para visualizar os dados/endereços de entrada e saída.

(2) No caso de duas ou mais funcionalidades serem ativadas simultaneamente o sistema deve apresentar um "E" piscando no display de saída de dados.

AULA - Dia 18/06/2014

Objetivo

- Avaliar miniprojeto 6

- Continuar desenvolvimento mini-projeto 7

AULA - Dia 25/06/2014

Objetivo

- Avaliar o miniprojeto 9

- Apresentar o Miniprojeto 8 envolvendo operações aritméticas e lógicas

Descrição do Miniprojeto 8

Acrescentar ao miniprojeto 7 três funconalidades adicionais:

- Operação de soma com dois operandos na memória RAM interna. Os dois endereços são fornecidos pelos barramentos de entrada e ao selecionar a opção de soma é mostrado na saída a soma dos operandos.

- Operação de and lógico byte a byte com dois operandos da memória RAM interna;

OBS: mostrar o estado do FLAG CARRY

Rascunho do Quadro

Referências

Arquivo:MIC-OperacoesArimeticas.pdf

AULA - Dia 25/06/2014

Exemplo do Professor

AULA - Dia 2/07/2014

Avaliação do Miniprojeto 7

Início do Miniprojeto 8

AULA DIA 3/7/2014

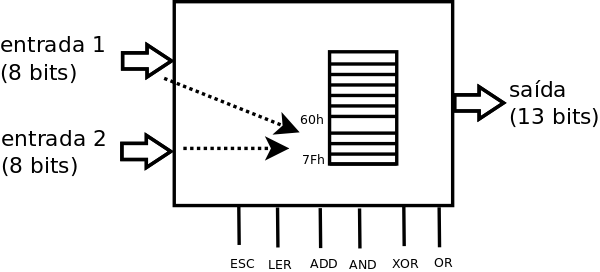

Projeto de Recuperação

Implementar um dispositivo capaz de interagir com um usuário no sentido de receber dados na sua memória RAM interna entre 60H e 7FH e apresentar a soma aritmética, a operação AND, OR e XORL de todos os bytes da RAM entre dois endereços fornecidos pelo usuário. A soma aritmética deve ser um número de 13 bits, portanto, a saida deve usar 8 bits de uma porta mais 5 bits de outra porta.

AULA DIA 9/7/2014

- Desenho ilustrativo do projeto de recuperação