Mudanças entre as edições de "DIG222802 AULA04"

| Linha 4: | Linha 4: | ||

| − | [[Imagem:fig24_DIG222802.png|center| | + | [[Imagem:fig24_DIG222802.png|center|600px]] |

<center> | <center> | ||

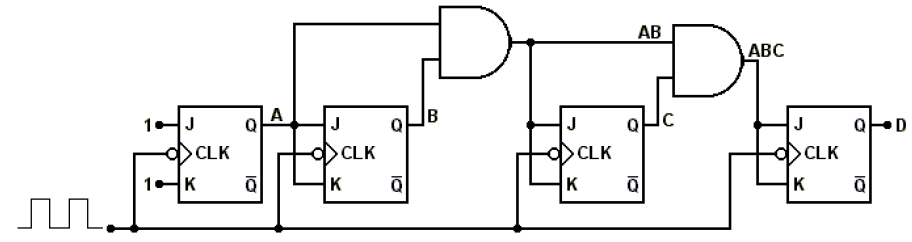

Figura 1 - Contador síncrono ascendente. | Figura 1 - Contador síncrono ascendente. | ||

Edição das 16h42min de 20 de abril de 2016

Contadores síncronos

Como vimos, o atraso de propagação dos FF nos contadores assíncronos limita a sua frequência máxima. Esse problema pode ser resolvido fazendo com que os FF mudem o estado de suas saídas no momento em que ocorre a transição de clock. Essa configuração caracteriza os contadores chamados de síncronos e é mostrada na Figura 1.

Figura 1 - Contador síncrono ascendente.

A análise da lógica do circuito do contador mostra que os FF do tipo JK somente estão no estado TOOGLE (J = 1 e K = 1) quando todas as saídas dos FF anteriores estão em nível ALTO. Como o sinal de clock é comum a todos os FF, o atraso de propagação do contador será o atraso de um FF somado ao atraso das portas AND.

- Atraso total ()

Lista de Exercícios

http://wiki.sj.ifsc.edu.br/images/2/2a/EX1_DIG222802.pdf

Referências

[1] Apostila do CURSO DE ELETRÔNICA DIGITAL. CEFET/SC: São José, 2011.

| << | <> | >> |

|---|