# **GD4017B** 5-STAGE JOHNSON COUNTER

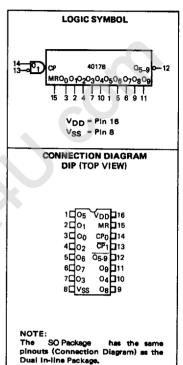

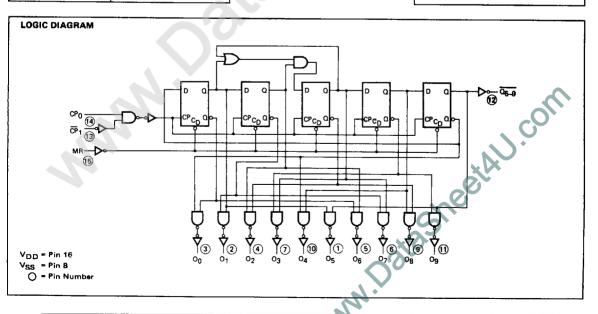

**DESCRIPTION** – The 4017B is a 5-Stage Johnson Decade Counter with ten glitch free decoded active HIGH Outputs  $(O_0$ – $O_0$ ), an active LOW Output from the most significant flip-flop  $(\overline{O_{5-9}})$ , active HIGH and active LOW Clock Inputs  $(CP_0, \overline{CP_1})$  and an overriding asynchronous Master Reset Input (MR).

The counter is advanced by either a LOW-to-HIGH transition at CP<sub>0</sub> while  $\overline{\text{CP}_1}$  is LOW or a HIGH-to-LOW transition at CP<sub>1</sub> while CP<sub>0</sub> is HIGH (see Functional Truth Table). When cascading 4017B counters, the  $Q_{5,9}$  output, which is LOW while the counter is in states 5, 6, 7, 8 and 9, can be used to drive the CP<sub>0</sub> input of the next 4017B.

A HIGH on the Master Reset Input (MR) resets the counter to zero ( $O_0 = \overline{Q_{5-9}} = \text{HIGH}$ ,  $O_1 - O_9 = \text{LOW}$ ) independent of the Clock Inputs (CP<sub>0</sub>,  $\overline{\text{CP}_1}$ ).

- TYPICAL COUNT FREQUENCY OF 13.8 MHz AT VDD = 10 V

- ACTIVE HIGH DECODED OUTPUTS

- TRIGGERS ON EITHER A HIGH-TO-LOW OR LOW-TO-HIGH TRANSITION

- CASCADABLE

#### PIN NAMES

CPO Clock Input (L→H Triggered)

CP1 Clock Input (H→L Triggered)

MR Master Reset Input

Mester Reset Input

Og Decoded Outputs

25-9 Carry Output (Active LOW)

### FUNCTIONAL TRUTH TABLE

| MR | CP <sub>0</sub> | CP <sub>1</sub>   | OPERATION                                                                  |

|----|-----------------|-------------------|----------------------------------------------------------------------------|

| Н  | x               | ×                 | O <sub>0</sub> = Q <sub>5-9</sub> = H; O <sub>1</sub> - O <sub>9</sub> = L |

| L  | н               | H→L               | Counter Advances                                                           |

| L  | L → H           | L                 | Counter Advances                                                           |

| L  | L               | x                 | No Change                                                                  |

| L  | X               | н                 | No Change                                                                  |

| L  | H               | $L \rightarrow H$ | No Change                                                                  |

| L  | H → L           | L                 | No Change                                                                  |

H = HIGH Level L = LOW Level

L→H = LOW-to-HIGH Transition H→L = HIGH-to-LOW Transition

X = Don't Care

## DC CHARACTERISTICS: V<sub>DD</sub> as shown, V<sub>SS</sub> = 0 V (See Note 1)

|        |                            | LIMITS     |                       |     |     |                        |     |                        |     | 1   |       |      |                 |                             |

|--------|----------------------------|------------|-----------------------|-----|-----|------------------------|-----|------------------------|-----|-----|-------|------|-----------------|-----------------------------|

| SYMBOL | PARAMETER                  |            | V <sub>DD</sub> = 5 V |     |     | V <sub>DD</sub> = 10 V |     | V <sub>DD</sub> = 15 V |     |     | UNITS | TEMP | TEST CONDITIONS |                             |

|        |                            |            | MIN                   | TYP | MAX | MIN                    | TYP | MAX                    | MIN | TYP | MAX   |      |                 |                             |

|        | Quiescent                  |            |                       |     | 20  |                        |     | 40                     |     |     | 80    |      | MIN, 25°C       |                             |

|        | Power<br>Supply<br>Current | xc         |                       |     | 150 |                        |     | 300                    |     |     | 600   | μА   | MAX             | All inputs at<br>0 V or VDD |

| ססי    |                            | · · · · AM |                       |     | 5   |                        |     | 10                     |     |     | 20    | μА   | MIN, 25°C       |                             |

|        |                            |            |                       |     | 150 |                        |     | 300                    |     |     | 600   |      | MAX             |                             |

# AC CHARACTERISTICS AND SET-UP REQUIREMENTS: $V_{DD}$ as shown, $V_{SS}$ = 0 V, $T_A$ = 25°C (See Note 2)

| SYMBOL           | PARAMETER                                           | LIMITS                |     |     |                        |      |     |                       |     |     |          |                         |

|------------------|-----------------------------------------------------|-----------------------|-----|-----|------------------------|------|-----|-----------------------|-----|-----|----------|-------------------------|

|                  |                                                     | V <sub>DD</sub> = 5 V |     |     | V <sub>DD</sub> = 10 V |      |     | V <sub>DD</sub> = 15V |     |     | UNITS    | TEST CONDITIONS         |

|                  |                                                     | MIN                   | TYP | MAX | MIN                    | TYP  | MAX | MIN                   | TYP | MAX | <u> </u> |                         |

| ™<br>tPLH        | Propagation Dalay,                                  |                       | 278 | 700 |                        | 114  | 285 |                       | 82  | 228 | ns       |                         |

| tPHL             | CPO or CP1 to On                                    |                       | 226 | 550 |                        | 94   | 240 |                       | 67  | 192 | ns       |                         |

| tPLH             | Propagation Delay,                                  |                       | 205 | 525 |                        | 87   | 225 |                       | 63  | 180 | ns       |                         |

| ФHL              | CPO or CP1 to Q5-9                                  |                       | 261 | 650 |                        | 105  | 250 |                       | 73  | 200 | ns       |                         |

| tPHL.            | Propegation Delay, MR to On                         |                       | 170 | 430 |                        | 80   | 175 |                       | 52  | 140 | ns       | ]                       |

| <sup>t</sup> PLH | Propagation Dalay, MR to Q5.9                       |                       | 125 | 300 |                        | 65   | 130 |                       | 40  | 104 | ns .     | CL = 50 pF,             |

| TLH              | Output Transition T!me                              |                       | 59  | 135 |                        | 31   | 70  |                       | 23  | 45  | ns       | R <sub>L</sub> = 200 kΩ |

| THL              |                                                     |                       | 63  | 135 |                        | 26   | 70  |                       | 19  | 45  | ns       |                         |

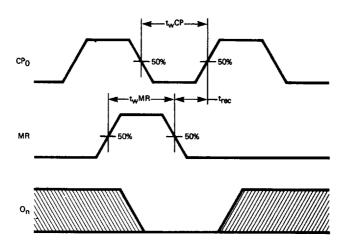

| twCP             | Min. CP <sub>0</sub> or CP <sub>1</sub> Pulse Width | 200                   | 85  |     | 70                     | 37   |     | 56                    | 28  |     | ns       | Times < 20 ns           |

| twMR             | Minimum MR Pulse Width                              | 130                   | 52  |     | 55                     | 22   |     | 44                    | 18  |     | ns       | 1111100 7 20 110        |

| t <sub>rec</sub> | MR Recovery Time                                    | 50                    | 16  |     | 25                     | 6    |     | 20                    | 3   |     | ns       |                         |

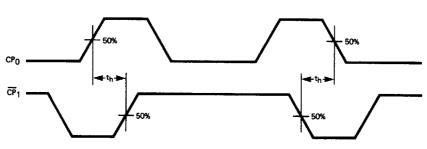

| th               | Hold Time, CP <sub>0</sub> to CP <sub>1</sub>       | 200                   | 90  |     | 90                     | 39   |     | 72                    | 26  |     | ns       |                         |

| th               | Hold Time, CP <sub>1</sub> to CP <sub>0</sub>       | 200                   | 89  |     | 90                     | 39   |     | 72                    | 22  |     | ns       |                         |

| fMAX             | Input Count Frequency (Note 3)                      | 2.5                   | 5.8 |     | 7                      | 13.8 |     | 8                     | 16  |     | MHz      |                         |

#### NOTES:

- 1. Additional DC Characteristics are listed in this section under 4000B Series CMOS Family Characteristics.

- 2. Propagation Delays and Output Transition Times are graphically described in this section under 4000B Series CMOS Family Characteristics.

- 3. For f<sub>MAX</sub>, input rise and fall times are greater than or equal to 5 ns and less than or equal to 20 ns.

4. It is recommended that input rise and fall times to either Clock input (CP<sub>0</sub> or CP<sub>1</sub>) be less than 15 µs at V<sub>DD</sub> = 5 V, 4 µs at V<sub>DD</sub> = 10 V, and 3  $\mu$ s at  $V_{DD}$  = 15 V.

### SWITCHING WAVEFORMS

HOLD TIMES, CPO TO CPT AND CPT TO CPO

Hold Times are shown as positive values, but may be specified as negative values.

# MINIMUM PULSE WIDTHS FOR CP AND MR AND RECOVERY TIME FOR MR

$\begin{array}{ll} \textbf{CONDITIONS: } \overline{CP_1} = \textbf{LOW while } CP_0 \text{ is triggered on a LOW-to-HIGH} \\ \textbf{transition. } t_wCP \text{ and } t_{rec} \text{ also apply when } CP_0 = \textbf{HIGH and } \overline{CP_1} \text{ is} \\ \textbf{triggered on a HIGH-to-LOW transition.} \end{array}$