# Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition User Guide

# **Design Recommendations**

Updated for Intel® Quartus® Prime Design Suite: 23.1

This document is part of a collection - <a href="Intel® Quartus® Prime Pro Edition User Guides - Combined">Intel® Quartus® Prime Pro Edition User Guides - Combined</a> PDF link

### **Contents**

| L. Re | ecommended HDL Coding Styles                                             | 4 |

|-------|--------------------------------------------------------------------------|---|

|       | 1.1. Using Provided HDL Templates                                        | 4 |

|       | 1.1.1. Inserting HDL Code from a Provided Template                       | 4 |

|       | 1.2. Instantiating IP Cores in HDL                                       | 5 |

|       | 1.3. Inferring Multipliers and DSP Functions                             | 5 |

|       | 1.3.1. Inferring Multipliers                                             |   |

|       | 1.3.2. Inferring Multiply-Accumulator and Multiply-Adder Functions       |   |

|       | 1.4. Inferring Memory Functions from HDL Code                            |   |

|       | 1.4.1. Inferring RAM functions from HDL Code                             |   |

|       | 1.4.2. Inferring ROM Functions from HDL Code                             |   |

|       | 1.4.3. Inferring Shift Registers in HDL Code                             |   |

|       | 1.4.4. Inferring FIFOs in HDL Code                                       |   |

|       | 1.5. Register and Latch Coding Guidelines                                |   |

|       | 1.5.1. Register Power-Up Values                                          |   |

|       | 1.5.2. Secondary Register Control Signals Such as Clear and Clock Enable |   |

|       | 1.5.3. Latches                                                           |   |

|       | 1.6. General Coding Guidelines                                           |   |

|       | 1.6.1. Tri-State Signals                                                 |   |

|       | 1.6.2. Clock Multiplexing                                                |   |

|       | 1.6.4. State Machine HDL Guidelines                                      |   |

|       | 1.6.5. Multiplexer HDL Guidelines                                        |   |

|       | 1.6.6. Cyclic Redundancy Check Functions                                 |   |

|       | 1.6.7. Comparator HDL Guidelines                                         |   |

|       | 1.6.8. Counter HDL Guidelines                                            |   |

|       | 1.7. Designing with Low-Level Primitives                                 |   |

|       | 1.8. Cross-Module Referencing (XMR) in HDL Code                          |   |

|       | 1.9. Using force Statements in HDL Code                                  |   |

|       | 1.10. Recommended HDL Coding Styles Revision History                     |   |

| _     |                                                                          |   |

| z. Re | ecommended Design Practices                                              |   |

|       | 2.1. Following Synchronous FPGA Design Practices                         |   |

|       | 2.1.1. Implementing Synchronous Designs                                  |   |

|       | 2.1.2. Asynchronous Design Hazards                                       |   |

|       | 2.2. HDL Design Guidelines                                               |   |

|       | 2.2.1. Considerations for the Intel Hyperflex FPGA Architecture          |   |

|       | 2.2.2. Optimizing Clocking Schomes                                       |   |

|       | 2.2.3. Optimizing Physical Implementation and Timing Closure             |   |

|       | 2.2.4. Optimizing Physical Implementation and Timing Closure             |   |

|       | 2.2.5. Optimizing Power Consumption                                      |   |

|       | 2.2.6. Managing Design Metastability                                     |   |

|       | 2.3. Use Clock and Register-Control Architectural Features               |   |

|       | 2.3.1. Use Global Reset Resources                                        |   |

|       | 2.3.2. Use Global Clock Network Resources                                |   |

|       | 2.3.4. Avoid Asynchronous Register Control Signals                       |   |

|       | 2.4. Implementing Embedded RAM                                           |   |

|       |                                                                          |   |

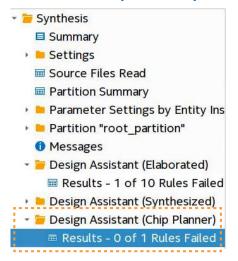

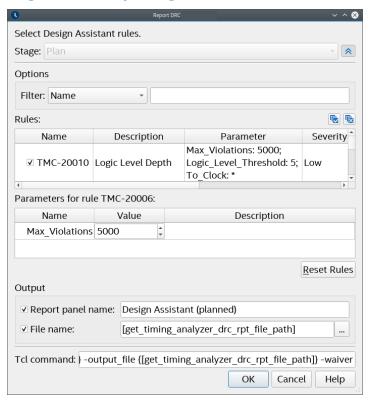

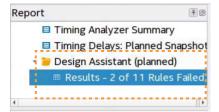

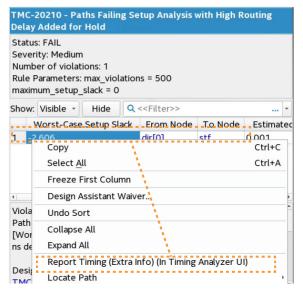

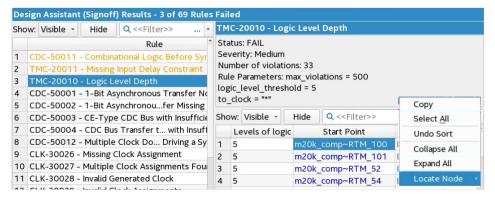

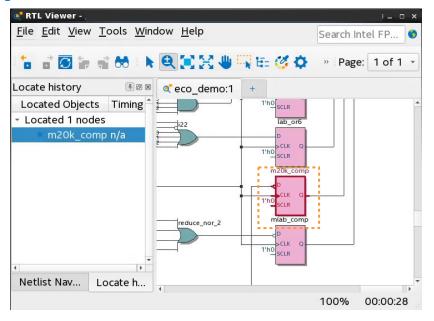

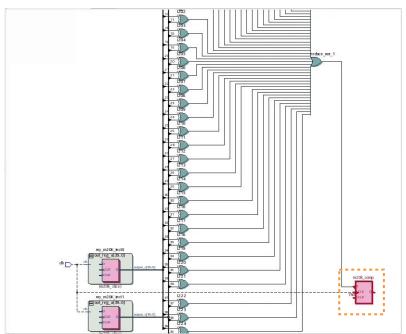

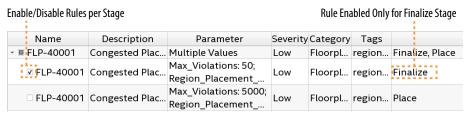

|              | 2.5. Design Assistant Design Rule Checking                                         | 96  |

|--------------|------------------------------------------------------------------------------------|-----|

|              | 2.5.1. Setting Up Design Assistant                                                 | 97  |

|              | 2.5.2. Running Design Assistant During Compilation                                 | 98  |

|              | 2.5.3. Running Design Assistant in Analysis Mode                                   |     |

|              | 2.5.4. Cross-Probing from Design Assistant                                         |     |

|              | 2.5.5. Managing Design Assistant Rules                                             | 107 |

|              | 2.5.6. Design Assistant Rule Categories                                            | 116 |

|              | 2.6. Recommended Design Practices Revision History                                 | 117 |

| 3. N         | Managing Metastability with the Intel Quartus Prime Software                       | 121 |

|              | 3.1. Metastability Analysis in the Intel Quartus Prime Software                    | 121 |

|              | 3.1.1. Data Synchronization Register Chains                                        |     |

|              | 3.1.2. Identify Synchronizers for Metastability Analysis                           |     |

|              | 3.1.3. How Timing Constraints Affect Synchronizer Identification and               |     |

|              | Metastability Analysis                                                             |     |

|              | 3.2. Metastability and MTBF Reporting                                              |     |

|              | 3.2.1. Metastability Reports                                                       |     |

|              | 3.2.2. Synchronizer Data Toggle Rate in MTBF Calculation                           |     |

|              | 3.3. MTBF Optimization                                                             |     |

|              | 3.3.1. Synchronization Register Chain Length                                       |     |

|              | 3.4. Reducing Metastability Effects                                                |     |

|              | 3.4.1. Apply Complete System-Centric Timing Constraints for the Timing Ana         |     |

|              | 3.4.2. Force the Identification of Synchronization Registers                       |     |

|              | 3.4.3. Set the Synchronizer Data Toggle Rate                                       |     |

|              | 3.4.4. Optimize Metastability During Fitting                                       |     |

|              | 3.4.5. Increase the Length of Synchronizers to Protect and Optimize                |     |

|              | 3.4.6. Increase the Number of Stages Used in Synchronizers                         |     |

|              | 3.4.7. Select a Faster Speed Grade Device                                          |     |

|              | 3.5. Scripting Support                                                             |     |

|              | 3.5.1. Identifying Synchronizers for Metastability Analysis                        |     |

|              | 3.5.2. Synchronizer Data Toggle Rate in MTBF Calculation                           |     |

|              | 3.5.3. report_metastability and Tcl Command                                        |     |

|              | 3.5.4. MTBF Optimization                                                           | 131 |

|              | 3.5.5. Synchronization Register Chain Length                                       |     |

|              | 3.6. Managing Metastability                                                        |     |

|              | 3.7. Managing Metastability with the Intel Quartus Prime Software Revision History |     |

| 4. 1         | Intel Quartus Prime Pro Edition User Guide: Design Recommendations Archive         | 134 |

| <b>A</b> . 1 | Intel Quartus Prime Pro Edition User Guides                                        | 135 |

|              |                                                                                    |     |

### 1. Recommended HDL Coding Styles

This chapter provides Hardware Description Language (HDL) coding style recommendations to ensure optimal synthesis results when targeting Intel FPGA devices.

HDL coding styles have a significant effect on the quality of results for programmable logic designs. Synthesis tools optimize HDL code for both logic utilization and performance; however, synthesis tools cannot interpret the intent of your design. Therefore, the most effective optimizations require conformance to recommended coding styles.

Note:

For style recommendations, options, or HDL attributes specific to your synthesis tool, refer to the synthesis tool vendor's documentation.

#### 1.1. Using Provided HDL Templates

The Intel® Quartus® Prime software provides templates for Verilog HDL, SystemVerilog, and VHDL templates to start your HDL designs. Many of the HDL examples in this document correspond with the **Full Designs** examples in the **Intel Quartus Prime Templates**. You can insert HDL code into your own design using the templates or examples.

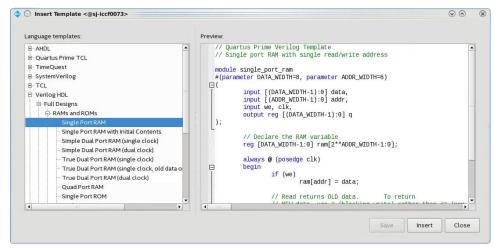

#### 1.1.1. Inserting HDL Code from a Provided Template

- 1. Click **File** ➤ **New**.

- In the New dialog box, select the HDL language for the design files: SystemVerilog HDL File, VHDL File, or Verilog HDL File; and click OK. A text editor tab with a blank file opens.

- 3. Right-click the blank file and click **Insert Template**.

- 4. In the **Insert Template** dialog box, expand the section corresponding to the appropriate HDL, then expand the **Full Designs** section.

- Select a template.

The template now appears in the **Preview** pane.

- To paste the HDL design into the blank Verilog or VHDL file you created, click Insert.

- 7. Click **Close** to close the **Insert Template** dialog box.

Figure 1. Inserting a RAM Template

Note:

Use the Intel Quartus Prime Text Editor to modify the HDL design or save the template as an HDL file to edit in your preferred text editor.

### 1.2. Instantiating IP Cores in HDL

Intel provides parameterizable IP cores that are optimized for Intel FPGA device architectures. Using IP cores instead of coding your own logic saves valuable design time.

Additionally, the Intel-provided IP cores offer more efficient logic synthesis and device implementation. Scale the IP core's size and specify various options by setting parameters. To instantiate the IP core directly in your HDL file code, invoke the IP core name and define its parameters as you would do for any other module, component, or sub design. Alternatively, you can use the IP Catalog (**Tools** > **IP Catalog**) and parameter editor GUI to simplify customization of your IP core variation. You can infer or instantiate IP cores that optimize device architecture features, for example:

- Transceivers

- LVDS drivers

- · Memory and DSP blocks

- Phase-locked loops (PLLs)

- Double-data rate input/output (DDIO) circuitry

For some types of logic functions, such as memories and DSP functions, you can infer device-specific dedicated architecture blocks instead of instantiating an IP core. Intel Quartus Prime synthesis recognizes certain HDL code structures and automatically infers the appropriate IP core or map directly to device atoms.

### 1.3. Inferring Multipliers and DSP Functions

The following sections describe how to infer multiplier and DSP functions from generic HDL code, and, if applicable, how to target the dedicated DSP block architecture in Intel FPGA devices.

#### **Related Information**

Intel FPGA Digital Signal Processing

#### 1.3.1. Inferring Multipliers

To infer multiplier functions, synthesis tools detect multiplier logic and implement this in Intel FPGA IP cores, or map the logic directly to device atoms.

For devices with DSP blocks, Intel Quartus Prime synthesis can implement the function in a DSP block instead of logic, depending on device utilization. The Intel Quartus Prime fitter can also place input and output registers in DSP blocks (that is, perform register packing) to improve performance and area utilization.

The following Verilog HDL and VHDL code examples show that synthesis tools can infer signed and unsigned multipliers as IP cores or DSP block atoms. Each example fits into one DSP block element. In addition, when register packing occurs, no extra logic cells for registers are required.

#### **Example 1. Verilog HDL Unsigned Multiplier**

```

module unsigned_mult (out, a, b);

output [15:0] out;

input [7:0] a;

input [7:0] b;

assign out = a * b;

endmodule

```

Note: The signed declaration in Verilog HDL is a feature of the Verilog 2001 Standard.

# Example 2. Verilog HDL Signed Multiplier with Input and Output Registers (Pipelining = 2)

```

module signed_mult (out, clk, a, b);

output [15:0] out;

input clk;

input signed [7:0] a;

input signed [7:0] b;

reg signed [7:0] a_reg;

reg signed [7:0] b_reg;

reg signed [15:0] out;

wire signed [15:0] mult_out;

assign mult_out = a_reg * b_reg;

always @ (posedge clk)

begin

a_reg <= a;

b_reg <= b;

out <= mult_out;</pre>

end

endmodule

```

#### **Example 3. VHDL Unsigned Multiplier with Input and Output Registers (Pipelining = 2)**

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY unsigned_mult IS

PORT (

a: IN UNSIGNED (7 DOWNTO 0);

```

```

b: IN UNSIGNED (7 DOWNTO 0);

clk: IN STD_LOGIC;

aclr: IN STD_LOGIC;

result: OUT UNSIGNED (15 DOWNTO 0)

END unsigned_mult;

ARCHITECTURE rtl OF unsigned_mult IS

SIGNAL a_reg, b_reg: UNSIGNED (7 DOWNTO 0);

BEGIN

PROCESS (clk, aclr)

BEGIN

IF (aclr ='1') THEN

a_reg <= (OTHERS => '0');

b_reg <= (OTHERS => '0');

result <= (OTHERS => '0');

ELSIF (rising_edge(clk)) THEN

a_reg <= a;

b_reg <= b;

result <= a_reg * b_reg;

END IF;

END PROCESS;

END rtl;

```

#### **Example 4. VHDL Signed Multiplier**

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY signed_mult IS

PORT (

a: IN SIGNED (7 DOWNTO 0);

b: IN SIGNED (7 DOWNTO 0);

result: OUT SIGNED (15 DOWNTO 0)

);

END signed_mult;

ARCHITECTURE rtl OF signed_mult IS

BEGIN

result <= a * b;

END rtl;

```

#### 1.3.2. Inferring Multiply-Accumulator and Multiply-Adder Functions

Synthesis tools detect multiply-accumulator or multiply-adder functions, and either implement them as Intel FPGA IP cores or map them directly to device atoms. During placement and routing, the Intel Quartus Prime software places multiply-accumulator and multiply-adder functions in DSP blocks.

Note:

Synthesis tools infer multiply-accumulator and multiply-adder functions only if the Intel device family has dedicated DSP blocks that support these functions.

A simple multiply-accumulator consists of a multiplier feeding an addition operator. The addition operator feeds a set of registers that then feeds the second input to the addition operator. A simple multiply-adder consists of two to four multipliers feeding one or two levels of addition, subtraction, or addition/subtraction operators. Addition is always the second-level operator, if it is used. In addition to the multiply-accumulator and multiply-adder, the Intel Quartus Prime Fitter also places input and output registers into the DSP blocks to pack registers and improve performance and area utilization.

Some device families offer additional advanced multiply-adder and accumulator functions, such as complex multiplication, input shift register, or larger multiplications.

The Verilog HDL and VHDL code samples infer multiply-accumulator and multiply-adder functions with input, output, and pipeline registers, as well as an optional asynchronous clear signal. Using the three sets of registers provides the best performance through the function, with a latency of three. To reduce latency, remove the registers in your design.

Note:

To obtain high performance in DSP designs, use register pipelining and avoid unregistered DSP functions.

#### **Example 5. Verilog HDL Multiply-Accumulator**

```

module sum_of_four_multiply_accumulate

#(parameter INPUT_WIDTH=18, parameter OUTPUT_WIDTH=44)

input clk, ena,

input [INPUT_WIDTH-1:0] dataa, datab, datac, datad,

input [INPUT_WIDTH-1:0] datae, dataf, datag, datah,

output reg [OUTPUT_WIDTH-1:0] dataout

// Each product can be up to 2*INPUT_WIDTH bits wide.

// The sum of four of these products can be up to 2 bits wider.

wire [2*INPUT_WIDTH+1:0] mult_sum;

// Store the results of the operations on the current inputs

// Store the value of the accumulation

always @ (posedge clk)

begin

if (ena == 1)

begin

dataout <= dataout + mult_sum;

end

endmodule

```

### 1.4. Inferring Memory Functions from HDL Code

The following coding recommendations provide portable examples of generic HDL code targeting dedicated Intel FPGA memory IP cores. However, if you want to use some of the advanced memory features in Intel FPGA devices, consider using the IP core directly so that you can customize the ports and parameters easily.

You can also use the Intel Quartus Prime templates provided in the Intel Quartus Prime software as a starting point.

Table 1. Intel Memory HDL Language Templates

| Language | Full Design Name                                                                                                                                                                              |      |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| VHDL     | Single-Port RAM Single-Port RAM with Initial Contents Simple Dual-Port RAM (single clock) Simple Dual-Port RAM (dual clock) True Dual-Port RAM (single clock) True Dual-Port RAM (dual clock) |      |

|          | conti                                                                                                                                                                                         | nued |

| Language      | Full Design Name                                                                                                                                                                                                            |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Mixed-Width RAM Mixed-Width True Dual-Port RAM Byte-Enabled Simple Dual-Port RAM Byte-Enabled True Dual-Port RAM Single-Port ROM Dual-Port ROM                                                                              |

| Verilog HDL   | Single-Port RAM Single-Port RAM with Initial Contents Simple Dual-Port RAM (single clock) Simple Dual-Port RAM (dual clock) True Dual-Port RAM (single clock) True Dual-Port RAM (dual clock) Single-Port ROM Dual-Port ROM |

| SystemVerilog | Mixed-Width Port RAM Mixed-Width True Dual-Port RAM Mixed-Width True Dual-Port RAM (new data on same port read during write) Byte-Enabled Simple Dual Port RAM Byte-Enabled True Dual-Port RAM                              |

#### **Related Information**

- Introduction to Intel® FPGA IP Cores

- Intel<sup>®</sup> Hyperflex<sup>™</sup> Architecture High-Performance Design Handbook

- Intel® Arria® 10 Core Fabric and General Purpose I/Os Handbook

#### 1.4.1. Inferring RAM functions from HDL Code

To infer RAM functions, synthesis tools recognize certain types of HDL code and map the detected code to technology-specific implementations. For device families that have dedicated RAM blocks, the Intel Quartus Prime software uses an Intel FPGA IP core to target the device memory architecture.

Synthesis tools typically consider all signals and variables that have a multidimensional array type and then create a RAM block, if applicable. This is based on the way the signals or variables are assigned or referenced in the HDL source description.

Standard synthesis tools recognize single-port and simple dual-port (one read port and one write port) RAM blocks. Some synthesis tools (such as the Intel Quartus Prime software) also recognize true dual-port (two read ports and two write ports) RAM blocks that map to the memory blocks in certain Intel FPGA devices.

Some tools (such as the Intel Quartus Prime software) also infer memory blocks for array variables and signals that are referenced (read/written) by two indexes, to recognize mixed-width and byte-enabled RAMs for certain coding styles.

Note:

If your design contains a RAM block that your synthesis tool does not recognize and infer, the design might require a large amount of system memory that can potentially cause compilation problems.

#### 1.4.1.1. Use Synchronous Memory Blocks

Memory blocks in Intel FPGA are synchronous. Therefore, RAM designs must be synchronous to map directly into dedicated memory blocks. For these devices, Intel Quartus Prime synthesis implements asynchronous memory logic in regular logic cells.

Synchronous memory offers several advantages over asynchronous memory, including higher frequencies and thus higher memory bandwidth, increased reliability, and less standby power. To convert asynchronous memory, move registers from the datapath into the memory block.

A memory block is synchronous if it has one of the following read behaviors:

- Memory read occurs in a Verilog HDL always block with a clock signal or a VHDL clocked process. The recommended coding style for synchronous memories is to create your design with a registered read output.

- Memory read occurs outside a clocked block, but there is a synchronous read address (that is, the address used in the read statement is registered). Synthesis does not always infer this logic as a memory block, or may require external bypass logic, depending on the target device architecture. Avoid this coding style for synchronous memories.

Note:

The synchronous memory structures in Intel FPGA devices can differ from the structures in other vendors' devices. For best results, match your design to the target device architecture.

This chapter provides coding recommendations for various memory types. All the examples in this document are synchronous to ensure that they can be directly mapped into the dedicated memory architecture available in Intel FPGAs.

#### 1.4.1.2. Avoid Unsupported Reset and Control Conditions

To ensure correct implementation of HDL code in the target device architecture, avoid unsupported reset conditions or other control logic that does not exist in the device architecture.

The RAM contents of Intel FPGA memory blocks cannot be cleared with a reset signal during device operation. If your HDL code describes a RAM with a reset signal for the RAM contents, the logic is implemented in regular logic cells instead of a memory block. Do not place RAM read or write operations in an always block or process block with a reset signal. To specify memory contents, initialize the memory or write the data to the RAM during device operation.

In addition to reset signals, other control logic can prevent synthesis from inferring memory logic as a memory block. For example, if you use a clock enable on the read address registers, you can alter the output latch of the RAM, resulting in the synthesized RAM result not matching the HDL description. Use the address stall feature as a read address clock enable to avoid this limitation. Check the documentation for your FPGA device to ensure that your code matches the hardware available in the device.

### Example 6. Verilog RAM with Reset Signal that Clears RAM Contents: Not Supported in Device Architecture

```

module clear_ram

(

input clock, reset, we,

input [7:0] data_in,

input [4:0] address,

output reg [7:0] data_out

);

reg [7:0] mem [0:31];

integer i;

always @ (posedge clock or posedge reset)

begin

if (reset == 1'b1)

mem[address] <= 0;

else if (we == 1'b1)

mem[address] <= data_in;

data_out <= mem[address];

end

endmodule</pre>

```

#### **Related Information**

Specifying Initial Memory Contents at Power-Up on page 24

#### 1.4.1.3. Check Read-During-Write Behavior

Ensure the read-during-write behavior of the memory block described in your HDL design is consistent with your target device architecture.

Your HDL source code specifies the memory behavior when you read and write from the same memory address in the same clock cycle. The read returns either the old data at the address, or the new data written to the address. This is referred to as the read-during-write behavior of the memory block. Intel FPGA memory blocks have different read-during-write behavior depending on the target device family, memory mode, and block type.

Synthesis tools preserve the functionality described in your source code. Therefore, if your source code specifies unsupported read-during-write behavior for the RAM blocks, the Intel Quartus Prime software implements the logic in regular logic cells as opposed to the dedicated RAM hardware.

#### Example 7. Continuous read in HDL code

One common problem occurs when there is a continuous read in the HDL code, as in the following examples. Avoid using these coding styles:

```

//Verilog HDL concurrent signal assignment

assign q = ram[raddr_reg];

-- VHDL concurrent signal assignment

q <= ram(raddr_reg);</pre>

```

This type of HDL implies that when a write operation takes place, the read immediately reflects the new data at the address independent of the read clock, which is the behavior of asynchronous memory blocks. Synthesis cannot directly map this behavior to a synchronous memory block. If the write clock and read clock are the

same, synthesis can infer memory blocks and add extra bypass logic so that the device behavior matches the HDL behavior. If the write and read clocks are different, synthesis cannot reliably add bypass logic, so it implements the logic in regular logic cells instead of dedicated RAM blocks. The examples in the following sections discuss some of these differences for read-during-write conditions.

In addition, the MLAB memories in certain device logic array blocks (LABs) does not easily support old data or new data behavior for a read-during-write in the dedicated device architecture. Implementing the extra logic to support this behavior significantly reduces timing performance through the memory.

Note:

For best performance in MLAB memories, ensure that your design does not depend on the read data during a write operation.

In many synthesis tools, you can declare that the read-during-write behavior is not important to your design (for example, if you never read from the same address to which you write in the same clock cycle). In Intel Quartus Prime Pro Edition synthesis, set the synthesis attribute ramstyle to no\_rw\_check to allow Intel Quartus Prime software to define the read-during-write behavior of a RAM, rather than use the behavior specified by your HDL code. This attribute can prevent the synthesis tool from using extra logic to implement the memory block, or can allow memory inference when it would otherwise be impossible.

#### 1.4.1.4. Controlling RAM Inference and Implementation

Intel Quartus Prime synthesis provides options to control RAM inference and implementation for Intel FPGA devices with synchronous memory blocks. Synthesis tools usually do not infer small RAM blocks because implementing small RAM blocks is more efficient if using the registers in regular logic.

To direct the Intel Quartus Prime software to infer RAM blocks globally for all sizes, enable the Allow Any RAM Size for Recognition option in the Advanced Analysis & Synthesis Settings dialog box (Assignments ➤ Settings ➤ Compiler Settings ➤ Synthesis Settings (Advanced)).

Alternatively, use the ramstyle RTL attribute to specify how an inferred RAM is implemented, including the type of memory block or the use of regular logic instead of a dedicated memory block. Intel Quartus Prime synthesis does not map inferred memory into MLABs unless the HDL code specifies the appropriate ramstyle attribute, although the Fitter may map some memories to MLABs.

Set the ramstyle attribute in the RTL or in the .qsf file.

```

(* ramstyle = "mlab" *) my_shift_reg

set_instance_assignment -name RAMSTYLE_ATTRIBUTE LOGIC -to ram

```

. This attribute controls the implementation of an inferred memory. Apply the attribute to a variable declaration that infers a RAM, ROM, or shift-register. Legal values are: "M9K", "M10K", "M20K", "M144K", "MLAB, "no\_rw\_check", "logic"

You can also specify the maximum depth of memory blocks for RAM or ROM inference in RTL. Specify the max\_depth synthesis attribute to the declaration of a variable that represents a RAM or ROM in your design file. For example:

```

// Limit the depth of the memory blocks implement "ram" to 512

// This forces the Intel Quartus Prime software to use two M512 blocks instead

of one M4K block to implement this RAM

(* max_depth = 512 *) reg [7:0] ram[0:1023];

```

In addition, you can specify the no\_ram synthesis attribute to prevent RAM inference on a specific array. For example:

```

(* no_ram *) logic [11:0] my_array [0:12];

```

# 1.4.1.5. Single-Clock Synchronous RAM with Old Data Read-During-Write Behavior

The code examples in this section show Verilog HDL and VHDL code that infers simple dual-port, single-clock synchronous RAM. Single-port RAM blocks use a similar coding style.

The read-during-write behavior in these examples is to read the old data at the memory address. For best performance in MLAB memories, use the appropriate attribute so that your design does not depend on the read data during a write operation. The simple dual-port RAM code samples map directly into Intel synchronous memory.

Single-port versions of memory blocks (that is, using the same read address and write address signals) allow better RAM utilization than dual-port memory blocks, depending on the device family. Refer to the appropriate device handbook for recommendations on your target device.

# Example 8. Verilog HDL Single-Clock, Simple Dual-Port Synchronous RAM with Old Data Read-During-Write Behavior

```

module single_clk_ram(

output reg [7:0] q,

input [7:0] d,

input [4:0] write_address, read_address,

input we, clk

);

reg [7:0] mem [31:0];

always @ (posedge clk) begin

if (we)

mem[write_address] <= d;

q <= mem[read_address]; // q doesn't get d in this clock cycle

end

endmodule</pre>

```

#### Example 9. VHDL Single-Clock, Simple Dual-Port Synchronous RAM with Old Data Read-During-Write Behavior

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY single_clock_ram IS

PORT (

clock: IN STD_LOGIC;

data: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

write_address: IN INTEGER RANGE 0 to 31;

read_address: IN INTEGER RANGE 0 to 31;

```

```

we: IN STD_LOGIC;

q: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

END single clock ram;

ARCHITECTURE rtl OF single_clock_ram IS

TYPE MEM IS ARRAY(0 TO 31) OF STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL ram_block: MEM;

BEGIN

PROCESS (clock)

IF (rising_edge(clock)) THEN

IF (we = '1') THEN

ram_block(write_address) <= data;</pre>

END IF;

q <= ram_block(read_address);</pre>

-- VHDL semantics imply that q doesn't get data

-- in this clock cycle

END IF;

END PROCESS;

END rtl;

```

Note:

The small size of this single\_clock\_ram causes the Compiler to infer the memory as MLAB memory blocks, rather than M20K memory blocks. If single\_clock\_ram specifies a larger width, the Compiler infers the memory as M20K memory blocks.

# 1.4.1.6. Single-Clock Synchronous RAM with New Data Read-During-Write Behavior

The examples in this section describe RAM blocks in which the read-during-write behavior returns the new value being written at the memory address.

To implement this behavior in the target device, synthesis tools add bypass logic around the RAM block. This bypass logic increases the area utilization of the design, and decreases the performance if the RAM block is part of the design's critical path. If the device memory supports new data read-during-write behavior when in single-port mode (same clock, same read address, and same write address), the Verilog memory block doesn't require any bypass logic. Refer to the appropriate device handbook for specifications on your target device.

The following examples use a blocking assignment for the write so that the data is assigned intermediately.

# Example 10. Verilog HDL Single-Clock, Simple Dual-Port Synchronous RAM with New Data Read-During-Write Behavior

#### Example 11. VHDL Single-Clock, Simple Dual-Port Synchronous RAM with New Data Read-During-Write Behavior:

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY single_clock_ram IS

PORT (

clock: IN STD_LOGIC;

data: IN STD_LOGIC_VECTOR (2 DOWNTO 0);

write_address: IN INTEGER RANGE 0 to 31;

read_address: IN INTEGER RANGE 0 to 31;

we: IN STD_LOGIC;

q: OUT STD_LOGIC_VECTOR (2 DOWNTO 0)

END single_clock_ram;

ARCHITECTURE rtl OF single_clock_ram IS

TYPE MEM IS ARRAY(0 TO 31) OF STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS (clock)

VARIABLE ram_block: MEM;

IF (rising_edge(clock)) THEN

IF (we = '1') THEN

ram_block(write_address) := data;

END IF;

q <= ram_block(read_address);</pre>

-- VHDL semantics imply that q doesn't get data

-- in this clock cycle

END IF;

END PROCESS;

END rtl;

```

It is possible to create a single-clock RAM by using an assign statement to read the address of mem and create the output q. By itself, the RTL describes new data readduring-write behavior. However, if the RAM output feeds a register in another hierarchy, a read-during-write results in the old data. Synthesis tools may not infer a RAM block if the tool cannot determine which behavior is described, such as when the memory feeds a hard hierarchical partition boundary. Avoid this type of RTL.

#### Example 12. Avoid Verilog Coding Style with Vague read-during-write Behavior

```

reg [7:0] mem [127:0];

reg [6:0] read_address_reg;

always @ (posedge clk) begin

if (we)

mem[write_address] <= d;

read_address_reg <= read_address;

end

assign q = mem[read_address_reg];</pre>

```

#### Example 13. Avoid VHDL Coding Style with Vague read-during-write Behavior

The following example uses a concurrent signal assignment to read from the RAM, and presents a similar behavior.

```

ARCHITECTURE rtl OF single_clock_rw_ram IS

TYPE MEM IS ARRAY(0 TO 31) OF STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL ram_block: MEM;

SIGNAL read_address_reg: INTEGER RANGE 0 to 31;

BEGIN

PROCESS (clock)

BEGIN

```

#### 1.4.1.7. Simple Dual-Port, Dual-Clock Synchronous RAM

With dual-clock designs, synthesis tools cannot accurately infer the read-during-write behavior because it depends on the timing of the two clocks within the target device. Therefore, the read-during-write behavior of the synthesized design is undefined and may differ from your original HDL code.

#### **Example 14. Verilog HDL Simple Dual-Port, Dual-Clock Synchronous RAM**

```

module simple_dual_port_ram_dual_clock

#(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=6)

(

input [(DATA_WIDTH-1):0] data,

input [(ADDR_WIDTH-1):0] read_addr, write_addr,

input we, read_clock, write_clock,

output reg [(DATA_WIDTH-1):0] q

);

// Declare the RAM variable

reg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];

always @ (posedge write_clock)

begin

// Write

if (we)

ram[write_addr] <= data;</pre>

end

always @ (posedge read_clock)

begin

// Read

q <= ram[read_addr];</pre>

end

endmodule

```

#### **Example 15. VHDL Simple Dual-Port, Dual-Clock Synchronous RAM**

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY dual_clock_ram IS

PORT (

clock1, clock2: IN STD_LOGIC;

data: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

write_address: IN INTEGER RANGE 0 to 31;

read_address: IN INTEGER RANGE 0 to 31;

we: IN STD LOGIC;

q: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

);

END dual_clock_ram;

ARCHITECTURE rtl OF dual_clock_ram IS

TYPE MEM IS ARRAY(0 TO 31) OF STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL ram_block: MEM;

SIGNAL read_address_reg : INTEGER RANGE 0 to 31;

```

683082 | 2023.08.03

```

PROCESS (clock1)

BEGIN

IF (rising_edge(clock1)) THEN

IF (we = '1') THEN

ram_block(write_address) <= data;</pre>

END IF;

END IF;

END PROCESS;

PROCESS (clock2)

BEGIN

IF (rising_edge(clock2)) THEN

q <= ram_block(read_address_reg);</pre>

read_address_reg <= read_address;</pre>

END IF;

END PROCESS;

END rtl;

```

#### **Related Information**

Check Read-During-Write Behavior on page 11

#### 1.4.1.8. True Dual-Port Synchronous RAM

The code examples in this section show Verilog HDL and VHDL code that infers true dual-port synchronous RAM. Different synthesis tools may differ in their support for these types of memories.

Intel FPGA synchronous memory blocks have two independent address ports, allowing for operations on two unique addresses simultaneously. A read operation and a write operation can share the same port if they share the same address.

The Intel Quartus Prime software infers true dual-port RAMs in Verilog HDL and VHDL, with the following characteristics:

- Any combination of independent read or write operations in the same clock cycle.

- At most two unique port addresses.

- In one clock cycle, with one or two unique addresses, they can perform:

- Two reads and one write

- Two writes and one read

- Two writes and two reads

In the synchronous RAM block architecture, there is no priority between the two ports. Therefore, if you write to the same location on both ports at the same time, the result is indeterminate in the device architecture. You must ensure your HDL code does not imply priority for writes to the memory block, if you want the design to be implemented in a dedicated hardware memory block. For example, if both ports are defined in the same process block, the code is synthesized and simulated sequentially so that there is a priority between the two ports. If your code does imply a priority, the logic cannot be implemented in the device RAM blocks and is implemented in regular logic cells. You must also consider the read-during-write behavior of the RAM block to ensure that it can be mapped directly to the device RAM architecture.

When a read and write operation occurs on the same port for the same address, the read operation may behave as follows:

- Read new data—Intel Arria<sup>®</sup> 10 and Intel Stratix<sup>®</sup> 10 devices support this behavior.

- Read old data—Not supported.

When a read and write operation occurs on different ports for the same address (also known as mixed port), the read operation may behave as follows:

- Read new data—Intel Quartus Prime Pro Edition synthesis supports this mode by creating bypass logic around the synchronous memory block.

- Read old data—Intel Arria 10 and Intel Cyclone® 10 devices support this behavior.

- **Read don't care**—Synchronous memory blocks support this behavior in simple dual-port mode.

The Verilog HDL single-clock code sample maps directly into synchronous Intel Arria 10 memory blocks. When a read and write operation occurs on the same port for the same address, the new data being written to the memory is read. When a read and write operation occurs on different ports for the same address, the old data in the memory is read. Simultaneous writes to the same location on both ports results in indeterminate behavior.

If you generate a dual-clock version of this design describing the same behavior, the inferred memory in the target device presents undefined mixed port read-during-write behavior, because it depends on the relationship between the clocks.

#### **Example 16. Verilog HDL True Dual-Port RAM with Single Clock**

```

/ Quartus Prime Verilog Template

// True Dual Port RAM with single clock

// Read-during-write behavior is undefined for mixed ports

// and "new data" on the same port

module true_dual_port_ram_single_clock

#(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=6)

input [(DATA_WIDTH-1):0] data_a, data_b,

input [(ADDR_WIDTH-1):0] addr_a, addr_b,

input we_a, we_b, clk,

output reg [(DATA_WIDTH-1):0] q_a, q_b

);

// Declare the RAM variable

reg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];

// Port A

always @ (posedge clk)

begin

if (we_a)

begin

ram[addr_a] = data_a;

end

q_a <= ram[addr_a];</pre>

// Port B

always @ (posedge clk)

begin

if (we_b)

begin

ram[addr_b] = data_b;

end

q_b <= ram[addr_b];</pre>

end

endmodule

```

#### **Example 17. VHDL Read Statement Example**

```

-- Port A

process(clk)

begin

if(rising\_edge(clk)) then

if(we_a = '1') then

ram(addr_a) := data_a;

end if;

q_a <= ram(addr_a);</pre>

end if;

end process;

-- Port B

process(clk)

begin

if(rising_edge(clk)) then

if(we_b = '1') then

ram(addr_b) := data_b;

end if;

q_b <= ram(addr_b);</pre>

end if;

end process;

```

The VHDL single-clock code sample maps directly into Intel FPGA synchronous memory. When a read and write operation occurs on the same port for the same address, the new data writing to the memory is read. When a read and write operation occurs on different ports for the same address, the behavior results in old data for Intel Arria 10 and Intel Cyclone 10 devices, and is undefined for Intel Stratix 10 devices. Simultaneous write operations to the same location on both ports results in indeterminate behavior.

If you generate a dual-clock version of this design describing the same behavior, the memory in the target device presents undefined mixed port read-during-write behavior because it depends on the relationship between the clocks.

#### **Example 18. VHDL True Dual-Port RAM with Single Clock**

```

-- Quartus Prime VHDL Template

-- True Dual-Port RAM with single clock

-- Read-during-write behavior is undefined for mixed ports

-- and "new data" on the same port

library ieee;

use ieee.std_logic_1164.all;

entity true_dual_port_ram_single_clock is

generic

DATA_WIDTH : natural := 8;

ADDR_WIDTH : natural := 6

);

port

clk

: in std_logic;

: in natural range 0 to 2**ADDR_WIDTH - 1;

addr_a

: in natural range 0 to 2**ADDR_WIDTH - 1;

addr_b

: in std_logic_vector((DATA_WIDTH-1) downto 0);

data a

: in std_logic_vector((DATA_WIDTH-1) downto 0);

data b

: in std_logic := '1';

: in std_logic := '1';

we_a

we_b

: out std_logic_vector((DATA_WIDTH -1) downto 0);

q_a

q_b

: out std_logic_vector((DATA_WIDTH -1) downto 0)

);

```

```

end true_dual_port_ram_single_clock;

architecture rtl of true_dual_port_ram_single_clock is

-- Build a 2-D array type for the RAM

subtype word_t is std_logic_vector((DATA_WIDTH-1) downto 0);

type memory_t is array(2**ADDR_WIDTH-1 downto 0) of word_t;

-- Declare the RAM

shared variable ram : memory_t;

begin

-- Port A

process(clk)

begin

if(rising_edge(clk)) then

if(we_a = '1') then

ram(addr_a) := data_a;

end if;

q_a <= ram(addr_a);</pre>

end if;

end process;

-- Port B

process(clk)

begin

if(rising_edge(clk)) then

if(we_b = '1') then

ram(addr_b) := data_b;

end if;

q_b <= ram(addr_b);</pre>

end if;

end process;

end rtl;

```

#### **Related Information**

Intel® Arria® 10 Core Fabric and General Purpose I/Os Handbook

#### 1.4.1.9. Mixed-Width Dual-Port RAM

The RAM code examples in this section show SystemVerilog and VHDL code that infers RAM with data ports with different widths.

Verilog-1995 doesn't support mixed-width RAMs because the standard lacks a multidimensional array to model the different read width, write width, or both. Verilog-2001 doesn't support mixed-width RAMs because this type of logic requires multiple packed dimensions. Different synthesis tools may differ in their support for these memories. This section describes the inference rules for Intel Quartus Prime Pro Edition synthesis.

The first dimension of the multi-dimensional packed array represents the ratio of the wider port to the narrower port. The second dimension represents the narrower port width. The read and write port widths must specify a read or write ratio supported by the memory blocks in the target device. Otherwise, the synthesis tool does not infer a RAM.

Refer to the Intel Quartus Prime HDL templates for parameterized examples with supported combinations of read and write widths. You can also find examples of true dual port RAMs with two mixed-width read ports and two mixed-width write ports.

#### Example 19. SystemVerilog Mixed-Width RAM with Read Width Smaller than Write Width

#### Example 20. SystemVerilog Mixed-Width RAM with Read Width Larger than Write Width

#### Example 21. VHDL Mixed-Width RAM with Read Width Smaller than Write Width

```

library ieee;

use ieee.std_logic_1164.all;

package ram_types is

type word_t is array (0 to 3) of std_logic_vector(7 downto 0);

type ram_t is array (0 to 255) of word_t;

end ram_types;

library ieee;

use ieee.std_logic_1164.all;

library work;

use work.ram_types.all;

entity mixed_width_ram is

we, clk : in std_logic;

waddr : in integer range 0 to 255;

wdata : in word_t;

raddr : in integer range 0 to 1023;

: out std_logic_vector(7 downto 0));

end mixed_width_ram;

architecture rtl of mixed_width_ram is

signal ram : ram_t;

begin -- rtl

process(clk, we)

begin

if(rising_edge(clk)) then

if(we = '1') then

```

```

ram(waddr) <= wdata;

end if;

q <= ram(raddr / 4 )(raddr mod 4);

end if;

end process;

end rtl;</pre>

```

#### Example 22. VHDL Mixed-Width RAM with Read Width Larger than Write Width

```

library ieee;

use ieee.std_logic_1164.all;

package ram_types is

type word_t is array (0 to 3) of std_logic_vector(7 downto 0);

type ram_t is array (0 to 255) of word_t;

end ram_types;

library ieee;

use ieee.std_logic_1164.all;

library work;

use work.ram_types.all;

entity mixed_width_ram is

port (

we, clk : in std_logic;

waddr : in integer range 0 to 1023;

wdata : in std_logic_vector(7 downto 0);

raddr : in integer range 0 to 255;

q : out word_t);

end mixed_width_ram;

architecture rtl of mixed_width_ram is

signal ram : ram_t;

begin -- rt.l

process(clk, we)

begin

if(rising_edge(clk)) then

if(we = '1') then

ram(waddr / 4)(waddr mod 4) <= wdata;</pre>

end if;

q <= ram(raddr);

end if;

end process;

end rtl;

```

#### 1.4.1.10. RAM with Byte-Enable Signals

The RAM code examples in this section show SystemVerilog and VHDL code that infers RAM with controls for writing single bytes into the memory word, or byte-enable signals.

Synthesis models byte-enable signals by creating write expressions with two indexes, and writing part of a RAM "word." With these implementations, you can also write more than one byte at once by enabling the appropriate byte enables.

Verilog-1995 doesn't support mixed-width RAMs because the standard lacks a multidimensional array to model the different read width, write width, or both. Verilog-2001 doesn't support mixed-width RAMs because this type of logic requires multiple packed dimensions. Different synthesis tools may differ in their support for these memories. This section describes the inference rules for Intel Quartus Prime Pro Edition synthesis.

Refer to the Intel Quartus Prime HDL templates for parameterized examples that you can use for different address widths, and true dual port RAM examples with two read ports and two write ports.

#### Example 23. SystemVerilog Simple Dual-Port Synchronous RAM with Byte Enable

```

module byte_enabled_simple_dual_port_ram

input we, clk,

input [ADDRESS_WIDTH-1:0] waddr, raddr,// address width = 6

input [NUM_BYTES-1:0] be, // 4 bytes per word

input [(BYTE_WIDTH * NUM_BYTES -1):0] wdata, // byte width = 8, 4 bytes per

output reg [(BYTE_WIDTH * NUM_BYTES -1):0] q // byte width = 8, 4 bytes per

word

);

parameter ADDRESS_WIDTH = 6;

parameter DEPTH = 2**ADDRESS_WIDTH;

parameter BYTE_WIDTH = 8;

parameter NUM_BYTES = 4;

// use a multi-dimensional packed array

//to model individual bytes within the word

logic [NUM_BYTES-1:0][BYTE_WIDTH-1:0] ram[0:DEPTH-1];

// # words = 1 << address width</pre>

// port A

always@(posedge clk)

begin

if(we) begin

for (int i = 0; i < NUM_BYTES; i = i + 1) begin

if(be[i]) ram[waddr][i] <= wdata[i*BYTE_WIDTH +: BYTE_WIDTH];</pre>

end

end

q <= ram[raddr];

end

endmodule

```

#### **Example 24. VHDL Simple Dual-Port Synchronous RAM with Byte Enable**

```

library ieee;

use ieee.std_logic_1164.all;

library work;

entity byte_enabled_simple_dual_port_ram is

generic (DEPTH : integer := 64;

NUM_BYTES : integer := 4;

BYTE_WIDTH : integer := 8

);

we, clk : in std_logic;

waddr, raddr : in integer range 0 to DEPTH -1;

-- address width = 6

be : in std_logic_vector (NUM_BYTES-1 downto 0); -- 4 bytes per word

wdata: in std_logic_vector((NUM_BYTES * BYTE_WIDTH -1) downto 0);

width = 32

q : out std_logic_vector((NUM_BYTES * BYTE_WIDTH -1) downto 0) ); --

width = 32

end byte_enabled_simple_dual_port_ram;

architecture rtl of byte_enabled_simple_dual_port_ram is

-- build up 2D array to hold the memory

type word_t is array (0 to NUM_BYTES-1) of std_logic_vector(BYTE_WIDTH-1

downto 0);

type ram_t is array (0 to DEPTH-1) of word_t;

signal ram : ram_t;

signal q_local : word_t;

```

```

begin -- Re-organize the read data from the RAM to match the output

unpack: for i in 0 to NUM_BYTES-1 generate

q(BYTE_WIDTH*(i+1) - 1 downto BYTE_WIDTH*i) <= q_local(i);</pre>

end generate unpack;

-- port A

process(clk)

begin

if(rising_edge(clk)) then

if(we = '1') then

for I in (NUM_BYTES-1) downto 0 loop

if(be(I) = '1') then

ram(waddr)(I) <= wdata(((I+1)*BYTE_WIDTH-1) downto</pre>

I*BYTE_WIDTH);

end if;

end loop;

end if;

q_local <= ram(raddr);</pre>

end if;

end process;

end rtl;

```

#### 1.4.1.11. Specifying Initial Memory Contents at Power-Up

Your synthesis tool may offer various ways to specify the initial contents of an inferred memory. There are slight power-up and initialization differences between dedicated RAM blocks and the MLAB memory, due to the continuous read of the MLAB.

Intel FPGA dedicated RAM block outputs always power-up to zero, and are set to the initial value on the first read. For example, if address 0 is pre-initialized to FF, the RAM block powers up with the output at 0. A subsequent read after power-up from address 0 outputs the pre-initialized value of FF. Therefore, if a RAM powers up and an enable (read enable or clock enable) is held low, the power-up output of 0 maintains until the first valid read cycle. The synthesis tool implements MLAB using registers that power-up to 0, but initialize to their initial value immediately at power-up or reset. Therefore, the initial value is seen, regardless of the enable status. The Intel Quartus Prime software maps inferred memory to MLABs when the HDL code specifies an appropriate ramstyle attribute.

In Verilog HDL, you can use an initial block to initialize the contents of an inferred memory. Intel Quartus Prime Pro Edition synthesis automatically converts the initial block into a Memory Initialization File (.mif) for the inferred RAM.

#### **Example 25. Verilog HDL RAM with Initialized Contents**

```

module ram_with_init(

output reg [7:0] q,

input [7:0] d,

input [4:0] write_address, read_address,

input we, clk

);

reg [7:0] mem [0:31];

integer i;

initial begin

for (i = 0; i < 32; i = i + 1)

mem[i] = i[7:0];

end

always @ (posedge clk) begin

if (we)

mem[write_address] <= d;</pre>

```

683082 | 2023.08.03

```

q <= mem[read_address];

end

endmodule</pre>

```

Intel Quartus Prime Pro Edition synthesis and other synthesis tools also support the \$readmemb and \$readmemh attributes. These attributes allow RAM initialization and ROM initialization work identically in synthesis and simulation.

#### **Example 26. Verilog HDL RAM Initialized with the readmemb Command**

```

reg [7:0] ram[0:15];

initial

begin

$readmemb("ram.txt", ram);

end

```

In VHDL, you can initialize the contents of an inferred memory by specifying a default value for the corresponding signal. Intel Quartus Prime Pro Edition synthesis automatically converts the default value into a .mif file for the inferred RAM.

#### **Example 27. VHDL RAM with Initialized Contents**

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

use ieee.numeric_std.all;

ENTITY ram_with_init IS

PORT(

clock: IN STD_LOGIC;

data: IN UNSIGNED (7 DOWNTO 0);

write_address: IN integer RANGE 0 to 31;

read_address: IN integer RANGE 0 to 31;

we: IN std logic;

q: OUT UNSIGNED (7 DOWNTO 0));

END;

ARCHITECTURE rtl OF ram_with_init IS

TYPE MEM IS ARRAY(31 DOWNTO 0) OF unsigned(7 DOWNTO 0);

FUNCTION initialize_ram

return MEM is

variable result : MEM;

BEGIN

FOR i IN 31 DOWNTO 0 LOOP

result(i) := to_unsigned(natural(i), natural'(8));

END LOOP;

RETURN result;

END initialize_ram;

SIGNAL ram_block : MEM := initialize_ram;

BEGIN

PROCESS (clock)

BEGIN

IF (rising_edge(clock)) THEN

IF (we = '1') THEN

ram_block(write_address) <= data;</pre>

END IF;

q <= ram_block(read_address);</pre>

END IF;

END PROCESS;

END rtl;

```

683082 | 2023.08.03

#### 1.4.2. Inferring ROM Functions from HDL Code

Synthesis tools infer ROMs when a CASE statement exists in which a value is set to a constant for every choice in the CASE statement.

Because small ROMs typically achieve the best performance when they are implemented using the registers in regular logic, each ROM function must meet a minimum size requirement for inference and placement in memory.

For device architectures with synchronous RAM blocks, to infer a ROM block, synthesis must use registers for either the address or the output. When your design uses output registers, synthesis implements registers from the input registers of the RAM block without affecting the functionality of the ROM. If you register the address, the power-up state of the inferred ROM can be different from the HDL design. In this scenario, Intel Quartus Prime synthesis issues a warning.

The following ROM examples map directly to the Intel FPGA memory architecture.

#### **Example 28. Verilog HDL Synchronous ROM**

#### **Example 29. VHDL Synchronous ROM**

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY sync_rom IS

PORT (

clock: IN STD_LOGIC;

address: IN STD_LOGIC_VECTOR(7 downto 0);

data_out: OUT STD_LOGIC_VECTOR(5 downto 0)

);

END sync_rom;

ARCHITECTURE rtl OF sync_rom IS

BEGIN

PROCESS (clock)

BEGIN

IF rising_edge (clock) THEN

CASE address IS

WHEN "00000000" => data_out <= "101111";

WHEN "00000001" => data_out <= "110110";

WHEN "11111110" => data_out <= "000001";

WHEN "11111111" => data_out <= "101010";

WHEN OTHERS

=> data_out <= "101111";

END CASE;

```

```

END IF;

END PROCESS;

END rtl;

```

#### **Example 30. Verilog HDL Dual-Port Synchronous ROM Using readmemb**

```

module dual_port_rom

#(parameter data_width=8, parameter addr_width=8)

input [(addr_width-1):0] addr_a, addr_b,

input clk,

output reg [(data_width-1):0] q_a, q_b

reg [data_width-1:0] rom[2**addr_width-1:0];

initial // Read the memory contents in the file

//dual_port_rom_init.txt.

begin

$readmemb("dual_port_rom_init.txt", rom);

end

always @ (posedge clk)

begin

q_a <= rom[addr_a];</pre>

q_b <= rom[addr_b];</pre>

end

endmodule

```

#### **Example 31. VHDL Dual-Port Synchronous ROM Using Initialization Function**

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity dual_port_rom is

generic (

DATA_WIDTH : natural := 8;

ADDR_WIDTH : natural := 8

);

port (

: in std_logic;

clk

addr_a : in natural range 0 to 2**ADDR_WIDTH - 1; addr_b : in natural range 0 to 2**ADDR_WIDTH - 1;

: out std_logic_vector((DATA_WIDTH -1) downto 0);

qа

: out std_logic_vector((DATA_WIDTH -1) downto 0)

);

end entity;

architecture rtl of dual_port_rom is

-- Build a 2-D array type for the ROM

subtype word_t is std_logic_vector((DATA_WIDTH-1) downto 0);

type memory_t is array(2**ADDR_WIDTH - 1 downto 0) of word_t;

function init rom

return memory_t is

variable tmp : memory_t := (others => '0'));

begin

for addr_pos in 0 to 2**ADDR_WIDTH - 1 loop

-- Initialize each address with the address itself

tmp(addr_pos) := std_logic_vector(to_unsigned(addr_pos, DATA_WIDTH));

end loop;

return tmp;

end init_rom;

-- Declare the ROM signal and specify a default initialization value.

signal rom : memory_t := init_rom;

begin

process(clk)

```

```

begin

if (rising_edge(clk)) then

q_a <= rom(addr_a);

q_b <= rom(addr_b);

end if;

end process;

end rtl;</pre>

```

#### 1.4.3. Inferring Shift Registers in HDL Code

The Intel Quartus Prime software Analysis & Synthesis stage of the Compiler automatically detects and infers shift registers in your HDL code according to the following guidelines:

- Shift Register Inference for Intel Stratix 10 and Intel Agilex<sup>™</sup> 7 Devices on page 29

- Shift Register Inference for Intel Arria 10 and Intel Cyclone 10 GX Devices on page 30

#### Shift Register Inference for Intel Stratix 10 and Intel Agilex<sup>™</sup> 7 Devices

Because of the high prevalence of registers in routing segments of the Intel Hyperflex<sup>™</sup> architecture, the Compiler's threshold for shift register inference is increased for Intel Stratix 10 and Intel Agilex<sup>™</sup> 7 devices. This increase in the threshold means that some logic that the Compiler infers as a shift register in a previous generation FPGA, may not be inferred as a shift register when targeting Intel Stratix 10 or Intel Agilex 7 devices. This threshold increase allows more register retiming, thus improving overall design performance.

The following criteria apply to shift register detection and inference for Intel Stratix 10 and Intel Agilex 7 devices.

# Default shift register inference requirements for Intel Stratix 10 and Intel Agilex 7 Devices:

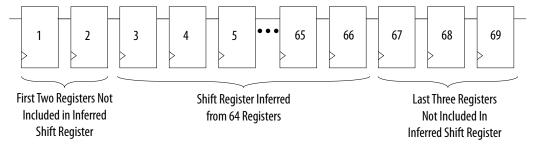

- 1. The minimum number of registers inferred in the shift register is 64. When the width of a chain of registers is 1, the chain must contain at least 69 registers for synthesis to infer a shift register. From these 69 registers, synthesis does not include the first and second registers in the chain in the inferred shift register. Synthesis places these first and second shift registers in ALMs. Synthesis infers a 64 bit long shift register with the third through sixty sixth registers. Synthesis does not include the last three registers in the chain in the inferred shift register. Rather, synthesis places the last three registers in ALMs.

- 2. The minimum depth of registers inferred in the shift register is 32. When the width of a chain of registers is two or more, the chain must contain at least 37 register levels for synthesis to infer a shift register. As in the first requirement, synthesis does not include the first and second registers levels in each chain in the inferred shift register, nor are the last three register levels.

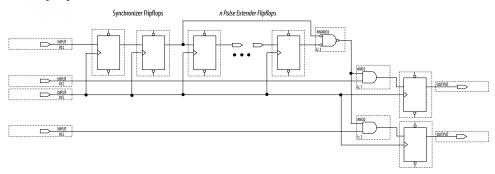

Figure 2. Shift Register Inference for Intel Stratix 10 and Intel Agilex 7 Devices

With the following assignment, the total number of required registers (depth \* width) drops to 37:

```

set_global_assignment -name ALLOW_ANY_SHIFT_REGISTER_SIZE_FOR_RECOGNITION ON

```

Note: An additional stage of inference takes place during the early retiming stage as physical synthesis optimization recovers area for registers that have not been retimed.

• With both of the following assignments, the total number of required registers (depth \* width) drops to 13:

```

set_global_assignment -name ALLOW_ANY_SHIFT_REGISTER_SIZE_FOR_RECOGNITION ON set_global_assignment -name PHYSICAL_SHIFT_REGISTER_INFERENCE=OFF

```

Note:

Reducing the shift register inference threshold can negatively impact design performance, as the technique reduces the number of registers available for retiming.

#### Shift Register Inference for Intel Arria 10 and Intel Cyclone 10 GX Devices

For Intel Arria 10 devices, Analysis & Synthesis detects a group of shift registers of the same length, and implements the registers using the Shift Register Intel FPGA IP.

For automatic detection, all of the shift registers must have the following characteristics:

- Use the same clock and clock enable

- Have no other secondary signals

- Have equally spaced taps that are at least three registers apart

Synthesis recognizes shift registers only for device families with dedicated RAM blocks. Intel Quartus Prime Pro Edition synthesis uses the following guidelines:

- The Intel Quartus Prime software determines whether to infer the Shift Register Intel FPGA IP based on the width of the registered bus (W), the length between each tap (L), or the number of taps (N).

- If the **Auto Shift Register Recognition** option is set to **Auto**, Intel Quartus Prime Pro Edition synthesis determines which shift registers are implemented in RAM blocks for logic by using the following methods:

- The Optimization Technique setting

- Logic and RAM utilization information about the design

- Timing information from Timing-Driven Synthesis

- If the registered bus width is one (W = 1), Intel Quartus Prime synthesis infers the shift register IP if the number of taps, times the length between each tap, is greater than or equal to 64  $(N \times L > 64)$ .

- If the registered bus width is greater than one (W > 1), and the registered bus width times the number of taps times the length between each tap is greater than or equal to 32  $(W \times N \times L > 32)$ , then Intel Quartus Prime synthesis the Shift Register Intel FPGA IP.

- If the length between each tap (L) is not a power of two, Intel Quartus Prime synthesis needs external logic (LEs or ALMs) to decode the read and write counters, because of different sizes of shift registers. This extra decode logic eliminates the performance and utilization advantages of implementing shift registers in memory.

683082 | 2023.08.03

The registers that Intel Quartus Prime synthesis maps to the Shift Register Intel FPGA IP, and places in RAM are not available in a Verilog HDL or VHDL output file for simulation tools, because their node names do not exist after synthesis.

Note:

The Compiler cannot implement a shift register that uses a shift enable signal into MLAB memory; instead, the Compiler uses dedicated RAM blocks. To control the type of memory structure that implements the shift register, use the ramstyle attribute. For example:

```

(* ramstyle = "mlab" *) my_shift_reg

```

#### 1.4.3.1. Simple Shift Register

The examples in this section show a simple, single-bit wide, 69-bit long shift register.

Intel Quartus Prime synthesis implements the register (W = 1 and M = 69) by using the Shift Register Intel FPGA IP, and maps it to RAM in the device, which may be placed in dedicated RAM blocks or MLAB memory. If the length of the register is less than 69 bits, Intel Quartus Prime synthesis implements the shift register in logic.

#### Example 32. Verilog HDL Single-Bit Wide, 69-Bit Long Shift Register

```

module shift_1x69 (clk, shift, sr_in, sr_out);

input clk, shift;

input sr_in;

output sr_out;

reg [68:0] sr;

always @ (posedge clk)

begin

if (shift == 1'b1)

begin

sr[68:1] <= sr[67:0];

sr[0] <= sr_in;

end

end

assign sr_out = sr[68];

endmodule</pre>

```

#### Example 33. VHDL Single-Bit Wide, 69-Bit Long Shift Register

```

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.all;

ENTITY shift_1x69 IS

PORT (

clk: IN STD LOGIC;

shift: IN STD_LOGIC;

sr_in: IN STD_LOGIC;

sr_out: OUT STD_LOGIC

END shift_1x69;

ARCHITECTURE arch OF shift_1x69 IS

TYPE sr_length IS ARRAY (68 DOWNTO 0) OF STD_LOGIC;

SIGNAL sr: sr_length;

BEGIN

PROCESS (clk)

BEGIN

IF (rising_edge(clk)) THEN

IF (shift = '1') THEN

sr(68 DOWNTO 1) <= sr(67 DOWNTO 0);

sr(0) <= sr_in;</pre>

END IF;

```

683082 | 2023.08.03

```

END IF;

END PROCESS;

sr_out <= sr(68);

END arch;</pre>

```

#### 1.4.3.2. Shift Register with Evenly Spaced Taps

The following examples show a Verilog HDL and VHDL 8-bit wide, 255-bit long shift register (W > 1 and M = 255) with evenly spaced taps at 64, 128, 192, and 254.

The synthesis software implements this function in a single ALTSHIFT\_TAPS IP core and maps it to RAM in supported devices, which is allowed placement in dedicated RAM blocks or MLAB memory.

#### Example 34. Verilog HDL 8-Bit Wide, 255-Bit Long Shift Register with Evenly Spaced Taps

```

module top (clk, shift, sr_in, sr_out, sr_tap_one, sr_tap_two,

sr_tap_three );

input clk, shift;

input [7:0] sr_in;

output [7:0] sr_tap_one, sr_tap_two, sr_tap_three, sr_out;

reg [7:0] sr [254:0];

integer n;

always @ (posedge clk)

begin

if (shift == 1'b1)

begin

for (n = 254; n>0; n = n-1)

begin

sr[n] \le sr[n-1];

end

sr[0] <= sr_in;</pre>

end

end

assign sr_tap_one = sr[64];

assign sr_tap_two = sr[128];

assign sr_tap_three = sr[192];

assign sr_out = sr[254];

endmodule

```

#### 1.4.4. Inferring FIFOs in HDL Code

There are various methods of implementing dual clock FIFOs, depending on the features needed in your design. The following dual clock FIFO example shows the basic FIFO functionality, with a design goal of high speed ( $f_{MAX}$ ) and small area.

The FIFO supports parameterization up to 32 words deep, and targets memory LABs (MLABs) for its memory block. Synthesis infers the MLABs from behavioral RTL in the generic\_mlab\_dc module.

Note:

If you don't want to code your own FIFO, you can parameterize the dual clock FIFO IP with the IP parameter editor in the Intel Quartus Prime software. Refer to the FIFO Intel FPGA IP User Guide.

#### **Related Information**

FIFO Intel FPGA IP User Guide

#### 1.4.4.1. Dual Clock FIFO Example in Verilog HDL

```

// Copyright 2021 Intel Corporation.

// This reference design file is subject licensed to you by the terms and

// conditions of the applicable License Terms and Conditions for Hardware

// Reference Designs and/or Design Examples (either as signed by you or

// found at https://www.altera.com/common/legal/leg-license_agreement.html ).

//

// As stated in the license, you agree to only use this reference design

// solely in conjunction with Intel FPGAs or Intel CPLDs.

// THE REFERENCE DESIGN IS PROVIDED "AS IS" WITHOUT ANY EXPRESS OR IMPLIED

// WARRANTY OF ANY KIND INCLUDING WARRANTIES OF MERCHANTABILITY,

// NONINFRINGEMENT, OR FITNESS FOR A PARTICULAR PURPOSE. Intel does not

// warrant or assume responsibility for the accuracy or completeness of any

// information, links or other items within the Reference Design and any

// accompanying materials.

//

// In the event that you do not agree with such terms and conditions, do not

// use the reference design file.

module dcfifo_example

parameter LOG_DEPTH

parameter WIDTH

= 20,

parameter ALMOST_FULL_VALUE = 30,

parameter ALMOST_EMPTY_VALUE = 2,

parameter NUM_WORDS = 2**LOG_DEPTH - 1,

parameter OVERFLOW_CHECKING = 0, // Overflow checking circuitry is \

using extra area. Use only if you need it

parameter UNDERFLOW_CHECKING = 0 // Underflow checking circuitry is \setminus

using extra area. Use only if you need it

input aclr,

input wrclk,

input wrreq,

input [WIDTH-1:0] data,

output reg wrempty,

output reg wrfull,

output reg wr_almost_empty,

output reg wr_almost_full,

output [LOG_DEPTH-1:0] wrusedw,

input rdclk,

input rdreq,

output [WIDTH-1:0] q,

output reg rdempty,

output reg rdfull,

output reg rd_almost_empty,

output reg rd_almost_full,

output [LOG_DEPTH-1:0] rdusedw

initial begin

if ((LOG_DEPTH > 5) | (LOG_DEPTH < 3))

$error("Invalid parameter value: LOG_DEPTH = %0d; valid range is 2 \

< LOG_DEPTH < 6", LOG_DEPTH);

$error("Incorrect parameter value: ALMOST_FULL_VALUE = %0d; valid \

range is 0 < ALMOST_FULL_VALUE < %0d"</pre>

ALMOST_FULL_VALUE, 2 ** LOG_DEPTH);

if ((ALMOST_EMPTY_VALUE > 2 ** LOG_DEPTH - 1) || (ALMOST_EMPTY_VALUE < 1))

$error("Incorrect parameter value: ALMOST_EMPTY_VALUE = %0d; valid \

range is 0 < ALMOST_EMPTY_VALUE < %0d",</pre>

```

```

ALMOST_EMPTY_VALUE, 2 ** LOG_DEPTH);

if ((NUM_WORDS > 2 ** LOG_DEPTH - 1) || (NUM_WORDS < 1))

$error("Incorrect parameter value: NUM_WORDS = %0d; \

valid range is 0 < NUM_WORDS < %0d",

NUM_WORDS, 2 ** LOG_DEPTH);

end

(* altera_attribute = "-name AUTO_CLOCK_ENABLE_RECOGNITION OFF" *) reg \

[LOG_DEPTH-1:0] write_addr = 0;

(* altera_attribute = "-name AUTO_CLOCK_ENABLE_RECOGNITION OFF" *) reg \

[LOG_DEPTH-1:0] read_addr = 0;

reg [LOG_DEPTH-1:0] wrcapacity = 0;

reg [LOG_DEPTH-1:0] rdcapacity = 0;

wire [LOG_DEPTH-1:0] wrcapacity_w;

wire [LOG_DEPTH-1:0] rdcapacity_w;

wire [LOG_DEPTH-1:0] rd_write_addr;

wire [LOG_DEPTH-1:0] wr_read_addr;

wire wrreq_safe;

wire rdreq_safe;

assign wrreq_safe = OVERFLOW_CHECKING ? wrreq & ~wrfull : wrreq;

assign rdreq_safe = UNDERFLOW_CHECKING ? rdreq & ~rdempty : rdreq;

initial begin

write_addr = 0;

read_addr = 0;

wrempty = 1;

wrfull = 0;

rdempty = 1;

rdfull = 0;

wrcapacity = 0;

rdcapacity = 0;

rd_almost_empty = 1;

rd_almost_full = 0;

wr_almost_empty = 1;

wr_almost_full = 0;

// ----- Write -----

add_a_b_s0_s1 #(LOG_DEPTH) wr_adder(

.a(write_addr),

.b(~wr_read_addr),

.s0(wrreq_safe),

.s1(1'b1),

.out(wrcapacity_w)

always @(posedge wrclk or posedge aclr) begin

if (aclr) begin

write_addr <= 0;</pre>

wrcapacity <= 0;

wrempty <= 1;

wrfull <= 0;

wr_almost_full <= 0;</pre>

wr_almost_empty <= 1;</pre>

end else begin

write_addr <= write_addr + wrreq_safe;</pre>

wrcapacity <= wrcapacity_w;</pre>

wrempty <= (wrcapacity == 0) && (wrreq == 0);

wrfull <= (wrcapacity == NUM_WORDS) || (wrcapacity == NUM_WORDS - 1) \</pre>

&& (wrreq == 1);

wr_almost_empty <=

(wrcapacity < (ALMOST_EMPTY_VALUE-1)) ||</pre>

(wrcapacity == (ALMOST_EMPTY_VALUE-1)) && (wrreq == 0);

```

```

wr_almost_full <=

(wrcapacity >= ALMOST_FULL_VALUE) ||

(wrcapacity == ALMOST_FULL_VALUE - 1) && (wrreq == 1);

end

end

assign wrusedw = wrcapacity;

// ----- Read -----

add_a_b_s0_s1 #(LOG_DEPTH) rd_adder(

.a(rd_write_addr),

.b(~read_addr),

.s0(1'b0),

.s1(~rdreq_safe),

.out(rdcapacity_w)

);

always @(posedge rdclk or posedge aclr) begin

if (aclr) begin

read_addr <= 0;

rdcapacity <= 0;

rdempty <= 1;

rdfull <= 0;

rd_almost_empty <= 1;

rd_almost_full <= 0;

end else begin

read_addr <= read_addr + rdreq_safe;</pre>

rdcapacity <= rdcapacity_w;

rdempty <= (rdcapacity == 0) || (rdcapacity == 1) && (rdreq == 1);

rdfull <= (rdcapacity == NUM_WORDS) && (rdreq == 0);

rd_almost_empty <=

(rdcapacity < ALMOST_EMPTY_VALUE) ||

(rdcapacity == ALMOST_EMPTY_VALUE) && (rdreq == 1);</pre>

rd_almost_full <=

(rdcapacity > ALMOST_FULL_VALUE) ||

(rdcapacity == ALMOST_FULL_VALUE) && (rdreq == 0);

end

end

assign rdusedw = rdcapacity;

// ----- Synchronizers -----

wire [LOG_DEPTH-1:0] gray_read_addr;

wire [LOG_DEPTH-1:0] wr_gray_read_addr;

wire [LOG_DEPTH-1:0] gray_write_addr;

wire [LOG_DEPTH-1:0] rd_gray_write_addr;

binary_to_gray #(.WIDTH(LOG_DEPTH)) rd_b2g (.clock(rdclk), .aclr(aclr), \

.din(read_addr), .dout(gray_read_addr));

synchronizer_ff_r2 #(.WIDTH(LOG_DEPTH)) rd2wr

(.din_clk(rdclk), .din(gray_read_addr), \

.dout_clk(wrclk), .dout(wr_gray_read_addr));

gray_to_binary #(.WIDTH(LOG_DEPTH)) rd_g2b (.clock(wrclk), .aclr(aclr), \

.din(wr_gray_read_addr), .dout(wr_read_addr));

binary_to_gray #(.WIDTH(LOG_DEPTH)) wr_b2g

(.clock(wrclk), .aclr(aclr), .din(write_addr), \

.dout(gray_write_addr));

synchronizer_ff_r2 #(.WIDTH(LOG_DEPTH)) wr2rd

(.din_clk(wrclk), .din(gray_write_addr), \

.dout_clk(rdclk), .dout(rd_gray_write_addr));

gray_to_binary #(.WIDTH(LOG_DEPTH)) wr_g2b (.clock(rdclk), .aclr(aclr), \

.din(rd_gray_write_addr), .dout(rd_write_addr));

// ----- MLAB -----

```

```

generic_mlab_dc #(.WIDTH(WIDTH), .ADDR_WIDTH(LOG_DEPTH)) mlab_inst (

.rclk(rdclk),

.wclk(wrclk),

.din(data),

.waddr(write_addr),

.we(1'b1),

.re(1'b1),

.raddr(read_addr),

.dout(q)

);

endmodule

module add_a_b_s0_s1 #(

parameter SIZE = 5

input [SIZE-1:0] a,

input [SIZE-1:0] b,

input s0,

input s1,

output [SIZE-1:0] out

);

wire [SIZE:0] left;

wire [SIZE:0] right;

wire temp;

assign left = \{a \ ^b, s0\};

assign right = \{a[SIZE-2:0] \ & b[SIZE-2:0], s1, s0\};

assign {out, temp} = left + right;

endmodule

module binary_to_gray #(

parameter WIDTH = 5

input clock,

input aclr,

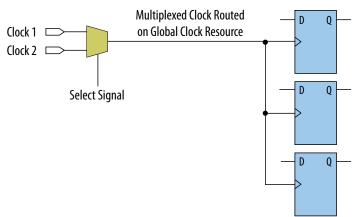

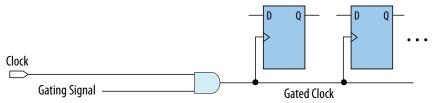

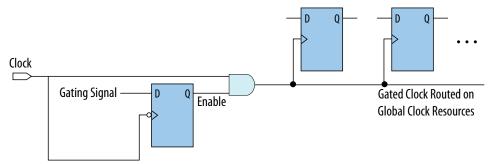

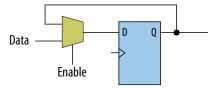

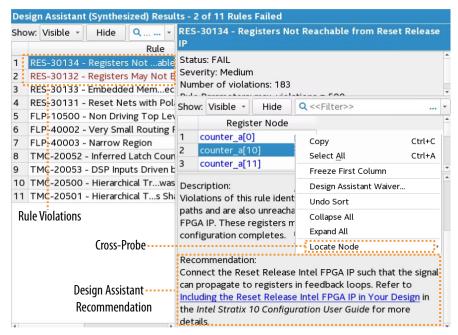

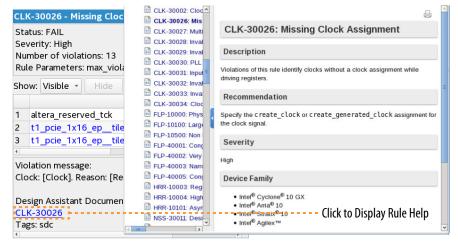

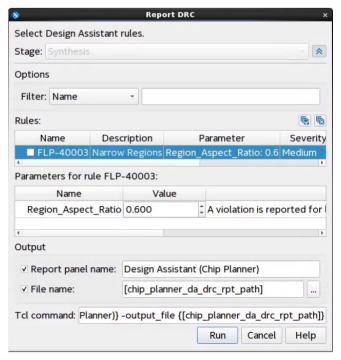

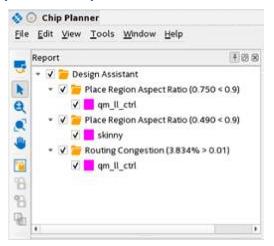

input [WIDTH-1:0] din,