Mudanças entre as edições de "Como as portas lógicas são implementadas com transistores CMOS"

Ir para navegação

Ir para pesquisar

| Linha 2: | Linha 2: | ||

*[https://tinyurl.com/2zzk9w4t Inversor] | *[https://tinyurl.com/2zzk9w4t Inversor] | ||

*[https://tinyurl.com/2nky5wkt Buffer] - Inversor + Inversor | *[https://tinyurl.com/2nky5wkt Buffer] - Inversor + Inversor | ||

| − | *[https://tinyurl.com/ | + | *[https://tinyurl.com/2pa9df5l porta NAND] |

*[https://tinyurl.com/2gjmndv6 porta AND] - NAND + Inversor | *[https://tinyurl.com/2gjmndv6 porta AND] - NAND + Inversor | ||

*[https://tinyurl.com/2mf4rktd porta NOR] | *[https://tinyurl.com/2mf4rktd porta NOR] | ||

Edição das 12h36min de 31 de março de 2023

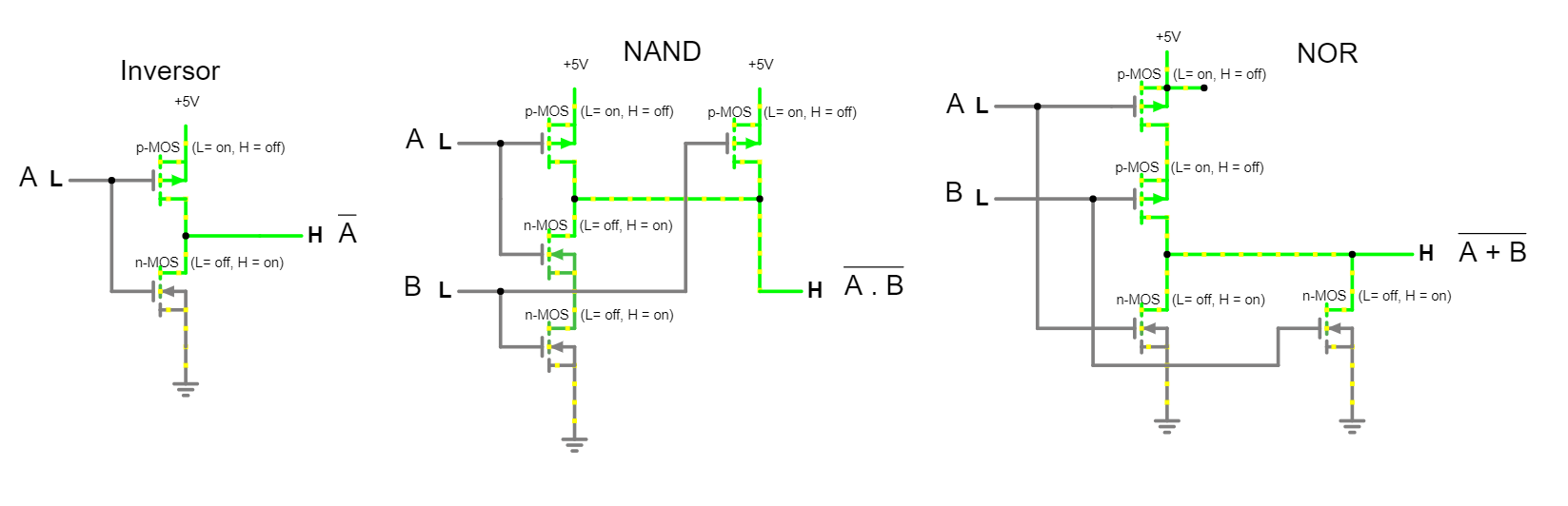

Utilizando o simulador FALSTAD, verifique o funcionamento das portas lógicas básicas construídas com transistores CMOS, e uma carga resistiva.

- Inversor

- Buffer - Inversor + Inversor

- porta NAND

- porta AND - NAND + Inversor

- porta NOR

- OR - NOR + Inversor

- porta XOR

- porta XNOR

Verifique como cada porta funciona. As tensões e correntes em cada transistor e da carga estão indicadas para observar o chaveamento dos transistores em cada estado. Lembre-se que L indica LOW (nível baixo, ou "0")e que H indica HIGH (nível alto, ou "1")