Mudanças entre as edições de "ELD129003-Engtelecom (Diário) - Prof. Marcos Moecke"

(→ATUAL) |

|||

| Linha 427: | Linha 427: | ||

;Encontro 7 (8 mar): | ;Encontro 7 (8 mar): | ||

* System on Chip | * System on Chip | ||

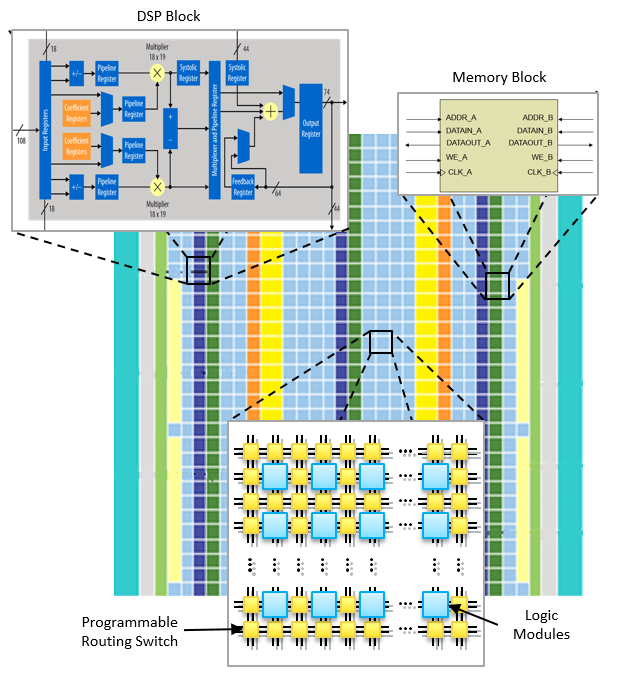

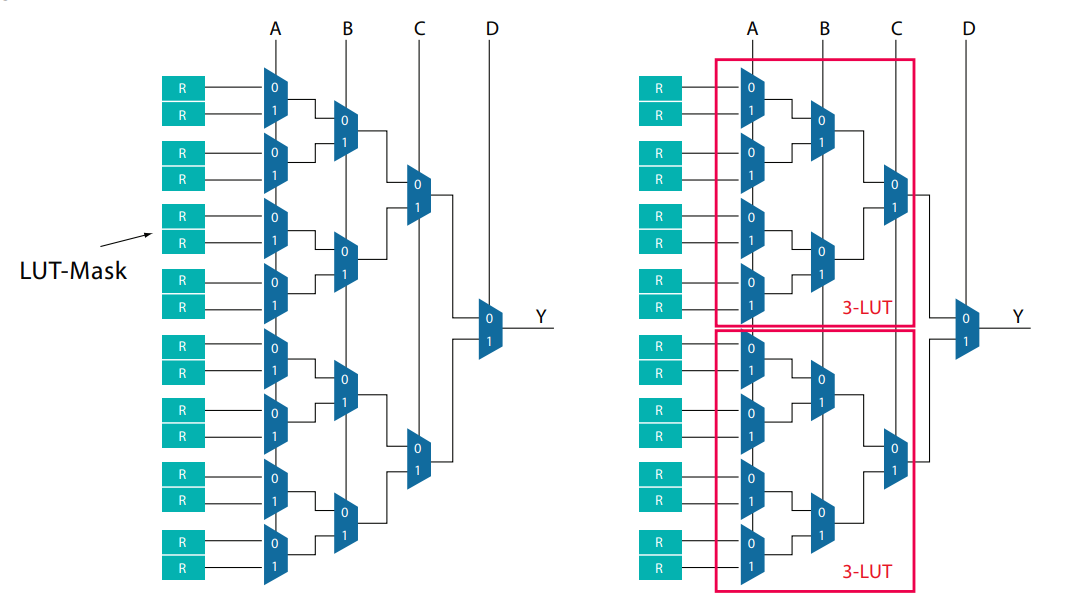

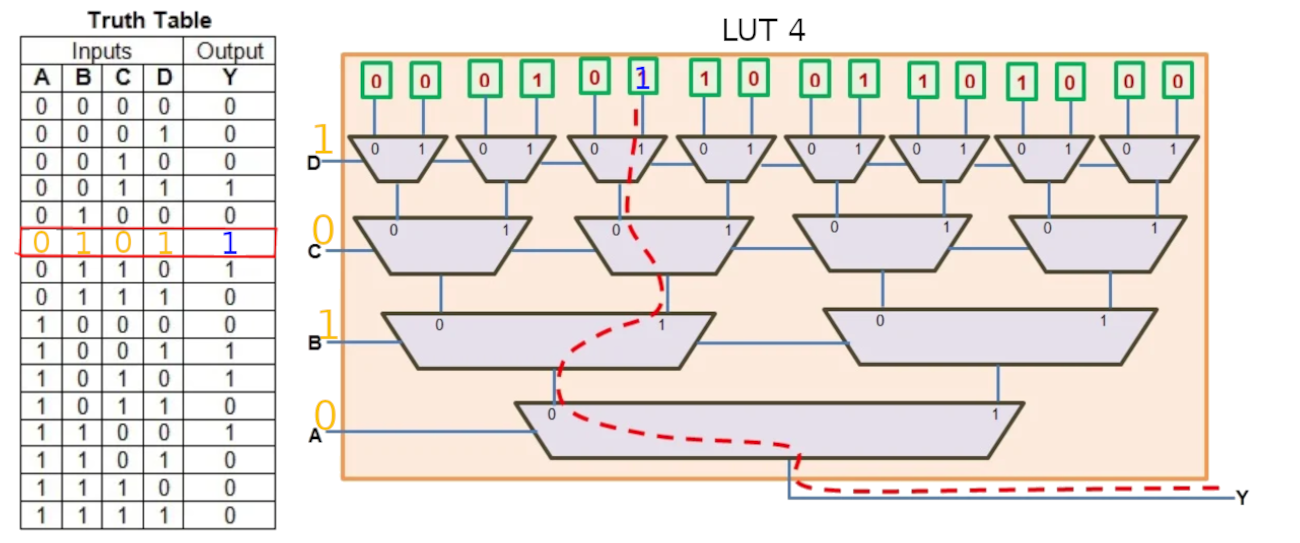

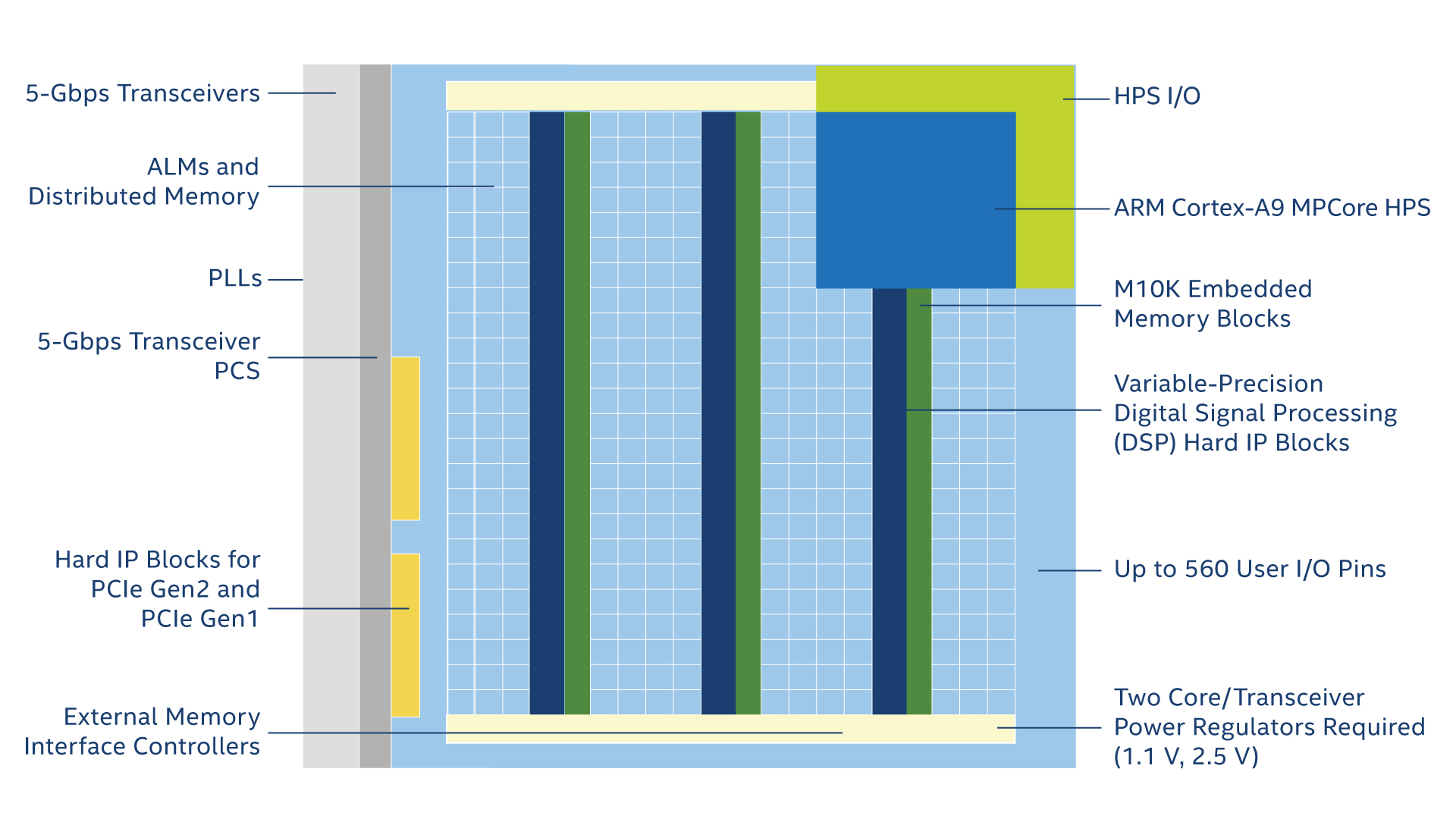

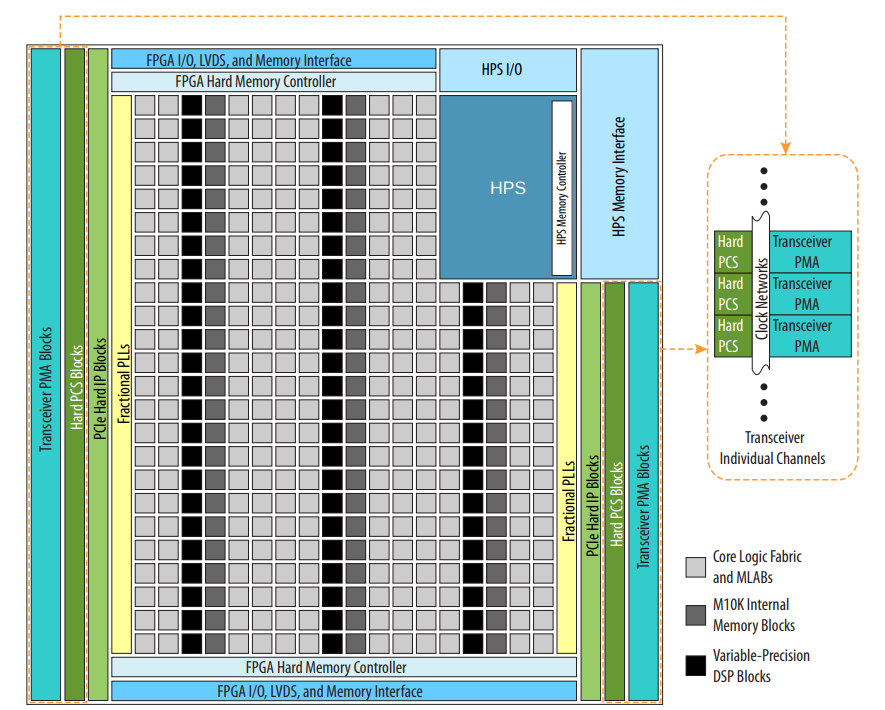

| − | {{fig|2.17| | + | {{fig|2.17|Altera - Visão geral do dispositivo Arria V SX e ST| ArriaV_SX_ST_Chip.png| 800 px | https://br.mouser.com/datasheet/2/612/av_51001-1623623.pdf}} |

| + | |||

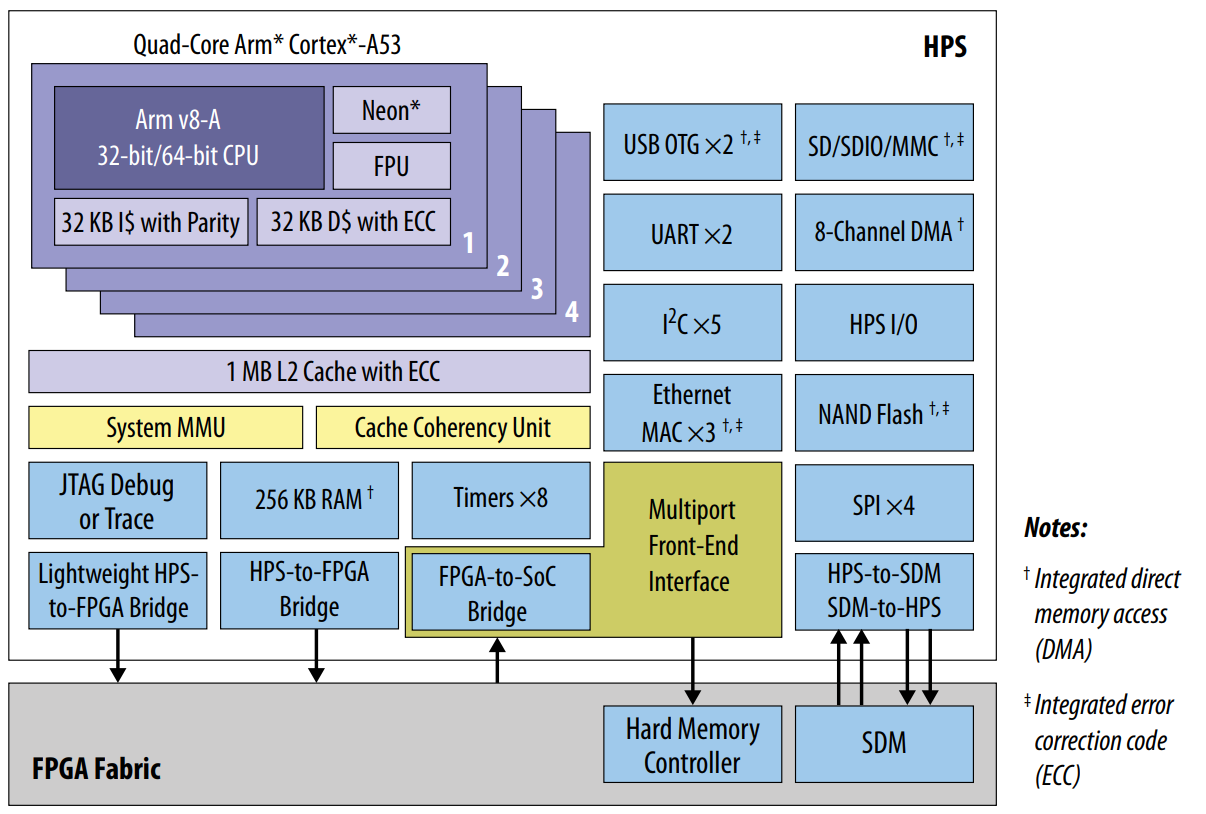

| + | {{fig|2.18|Altera - Agilex 7 SoCs HPS Digrama de Blocos| Agilex7SoC_Blocos.png| 800 px | https://static6.arrow.com/aropdfconversion/b568cfe009abfed6a28eff56700189883d7fc179/ag-overview-683458-666707.pdf}} | ||

* [https://wiki.sj.ifsc.edu.br/index.php/ELD129003-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE1_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis AE1 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 a 4 | * [https://wiki.sj.ifsc.edu.br/index.php/ELD129003-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE1_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis AE1 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 a 4 | ||

| Linha 437: | Linha 439: | ||

::*[https://www.newark.com/ Newark] | ::*[https://www.newark.com/ Newark] | ||

:* Fabricantes de DLPs/FPGAs e familias de DLPs atuais. | :* Fabricantes de DLPs/FPGAs e familias de DLPs atuais. | ||

| − | ::*[https://www.altera.com/products/fpga/overview.html ALTERA/INTEL] - Stratix, Arria, Cyclone, Max | + | ::*[https://www.altera.com/products/fpga/overview.html ALTERA/INTEL] - Stratix, Arria, Cyclone, Max, Agilex |

::*[https://www.xilinx.com/products/silicon-devices/fpga.html Xilinx/AMD] - Virtex, Kintex, Artix, Zynq (SoC) | ::*[https://www.xilinx.com/products/silicon-devices/fpga.html Xilinx/AMD] - Virtex, Kintex, Artix, Zynq (SoC) | ||

::*[https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas Microchip] - Igloo, PolarFire | ::*[https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas Microchip] - Igloo, PolarFire | ||

Edição das 09h32min de 8 de março de 2024

Registro on-line das aulas

Unidade 1 - Aula inicial, Introdução a disciplina

- 1 ENCONTRO

| Unidade 1 - Aula inicial, Introdução a disciplina |

|---|

|

Unidade REV - PRIMEIRO CONTATO COM VHDL

- 3 ENCONTROS

| Unidade REV - PRIMEIRO CONTATO COM VHDL | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

Para ilustrar essas instruções utilizaremos o exemplo de um Mux4x1. Um multiplexador digital de N entradas e 1 saída, frequentemente abreviado como MUX N:1, é um circuito digital muito utilizado para rotear sinais digitais. Ele desempenha a função de selecionar uma das entradas para ser encaminhada para a saída com base em um sinal de seleção (ou controle).

Dada a função booleana do MUX4:1 é simples para descreve-lo em VHDL utilizando apenas operadores lógicos. entity mux4x1 is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

Sel : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity;

-- Implementação com lógica pura

architecture v_logica_pura of mux4x1 is

begin

Y <= (X(0) and (not Sel(1)) and (not Sel(0))) or

...

end architecture;

No entanto, o MUX4:1 também pode ser descrito utilizando a instrução WHEN-ELSE <optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

...

<value> else

<value>;

Warning (13012): Latch ... has unsafe behavior

No caso do MUX4:1 ele poderia ser descrito como: -- Implementação com WHEN ELSE

architecture v_WHEN_ELSE of mux4x1 is

begin

Y <= X(0) when Sel = "00" else

X(1) when Sel = "01" else

X(2) when Sel = "10" else

X(3);

end architecture;

Outra forma de descrever o MUX4:1 seria utilizando a instrução WITH-SELECT <optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

Error (10313): VHDL Case Statement error ...: Case Statement choices must cover all possible values of expression

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux4x1 is

begin

with Sel select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture;

CONFIGURATION <configuration_name> OF <entity_name> IS

FOR <architecture_name> END FOR;

END CONFIGURATION;

-- Design Unit que associa a architecture com a entity

CONFIGURATION cfg_ifsc OF mux4x1 IS

FOR v_logica_pura END FOR;

-- FOR v_WHEN_ELSE END FOR;

-- FOR v_WITH_SELECT END FOR;

END CONFIGURATION;

Figura 2.1 - Código RTL do mux4x1 v_logica_pura  Figura 2.2 - Código RTL do mux4x1 v_WHEN_ELSE  Figura 2.3 - Código RTL do mux4x1 v_WITH_SELECT

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Unidade 2 - Dispositivos Lógicos Programáveis

- 3 ENCONTROS

| Unidade REV - PRIMEIRO CONTATO COM VHDL | ||

|---|---|---|

AvaliaçõesDurante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

Atividade relâmpago (AR)As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Atividade extra-classe (AE)A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo. AE1 - Conhecendo os dispositivos lógicos programáveis

Referências Bibliográficas:

|