Mudanças entre as edições de "Experimento 16 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| (4 revisões intermediárias por um outro usuário não estão sendo mostradas) | |||

| Linha 6: | Linha 6: | ||

* Fazer a simulação temporal do circuito com o QSIM; | * Fazer a simulação temporal do circuito com o QSIM; | ||

* Preparar o circuito lógico para gravação em um kit de desenvolvimento; | * Preparar o circuito lógico para gravação em um kit de desenvolvimento; | ||

| − | |||

| − | |||

;Materiais necessários: | ;Materiais necessários: | ||

#[http://www.ti.com/lit/ds/symlink/sn74284.pdf 74X284/285 Multiplicador 4x4] (disponível na biblioteca da ALTERA) | #[http://www.ti.com/lit/ds/symlink/sn74284.pdf 74X284/285 Multiplicador 4x4] (disponível na biblioteca da ALTERA) | ||

| Linha 18: | Linha 16: | ||

[[Imagem:Exp16_diag.png|600px|center]] | [[Imagem:Exp16_diag.png|600px|center]] | ||

| − | Após salvar o arquivo como multiplicador_comercial.bdf em uma pasta vazia com nome Exp16, e crie um projeto multiplicador_comercial.qpf utilizando a família family='''Cyclone | + | Após salvar o arquivo como multiplicador_comercial.bdf em uma pasta vazia com nome Exp16, e crie um projeto multiplicador_comercial.qpf utilizando a família family='''Cyclone''' com o dispositivo device='''EP1C3T100A8'''. Após isso compile o projeto. |

| − | ==Gerar formas de onda para entrada de simulação | + | ==Gerar formas de onda para entrada de simulação== |

*Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome EntradaFunc.vwf. | *Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome EntradaFunc.vwf. | ||

| − | [[Imagem:Exp16_entrada.png| | + | [[Imagem:Exp16_entrada.png|900px]] |

==Fazer a simulação temporal do circuito com o QSIM== | ==Fazer a simulação temporal do circuito com o QSIM== | ||

*Faça a simulação temporal do circuito e verifique o resultado obtido do circuito implementado. | *Faça a simulação temporal do circuito e verifique o resultado obtido do circuito implementado. | ||

| − | [[Imagem:Exp16_saidaTemp.png| | + | [[Imagem:Exp16_saidaTemp.png|900px]] |

| − | * | + | *Através do uso de cursores, meça os atrasos de propagação apresentados no circuito. |

==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ||

| + | Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2-115. | ||

| + | *Mude a família e dispositivo a ser usado ('''Assignments > Devices'''), [Family = '''Cyclone IV E'''] e selecione '''EP4CE22F17C7N''' | ||

| + | *Faça uma nova Análise e Sintese ('''Processing > Start > Start Analysis & Synthesis''') para trocar de Device | ||

| + | *Abra o Pin Planner ('''Assignments > Pin_Planner''') e atribua os pinos conforme a [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf pinagem do kit DE2-115]. | ||

| + | Kamila, aqui estava errado: precisas corrigir nos outros se tiver o mesmo erro. EP4CE22F17C6N e | ||

| + | faltou também indicar: | ||

| + | * Faça uma nova Análise e Sintese (Processing > Start > Start Analysis & Synthesis) para trocar de Device | ||

| + | * Abra o Pin Planner (Assignments > Pin_Planner) --[[Usuário:Moecke|Marcos Moecke]] 10h57min de 6 de outubro de 2015 (BRT) | ||

| − | = | + | *Atribua os pinos conforme a [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf pinagem do kit DE2-115]. |

| − | + | *Utilize os leds verdes para indicar a saída. | |

| − | + | *Utilize os switches para indicar as entradas. | |

| + | *Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem: | ||

| + | [[Imagem:Exp16_pinagem.png|300px|center]] | ||

| + | *Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: '''As input tri-stated'''. [OK]. | ||

| + | *Compile o projeto e verifique se os pinos também aparecem no diagrama esquemático. | ||

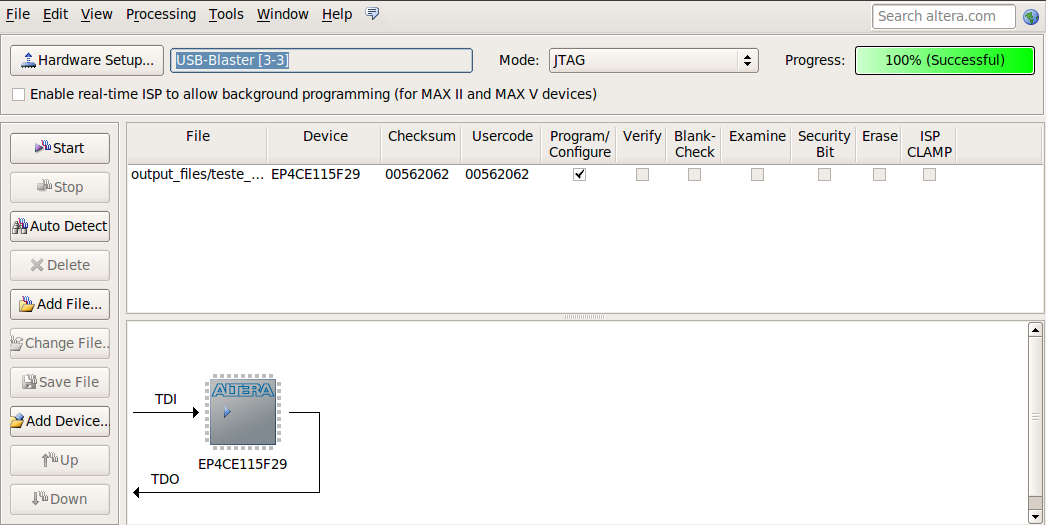

| + | *No Quartus vá em ('''Tools > Programmer''') para abrir a página de programação; | ||

| + | **Selecione o Hardware (Hardware Setup > '''USB-Blaster'''); | ||

| + | **Utilize o modo JTAG e clique em Start para começar a programação; [[Arquivo:Programador.png|200px|thumb|Clique para Ampliar]] | ||

| + | *Verifique os resultados obtidos. | ||

Edição atual tal como às 10h57min de 6 de outubro de 2015

Multiplicador (Comercial)

- Objetivos

- Compreender o funcionamento multiplicador binário de 4 bits por 4 bits;

- Gerar formas de onda para entrada de simulação;

- Fazer a simulação temporal do circuito com o QSIM;

- Preparar o circuito lógico para gravação em um kit de desenvolvimento;

- Materiais necessários

- 74X284/285 Multiplicador 4x4 (disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

- Kit DE2-115

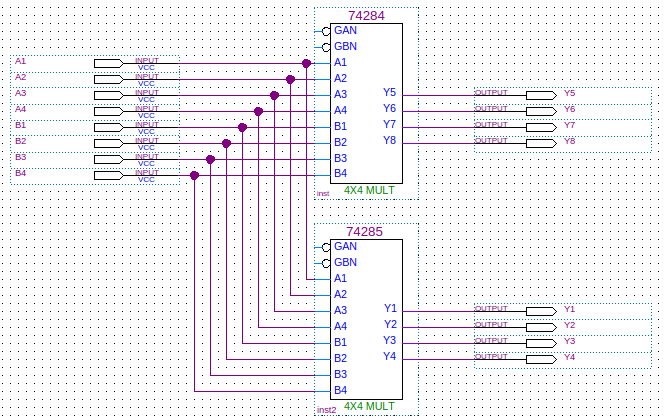

Diagrama esquemático

- Abra o Quartus II (versão 13.0.1 SE) e insira o diagrama esquemático de um multiplicador binário de 4 bits por 4 bits, conforme a figura abaixo.

Após salvar o arquivo como multiplicador_comercial.bdf em uma pasta vazia com nome Exp16, e crie um projeto multiplicador_comercial.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso compile o projeto.

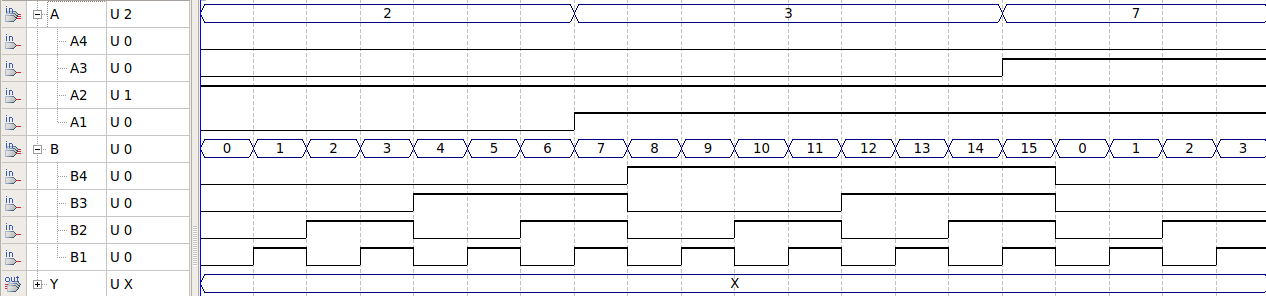

Gerar formas de onda para entrada de simulação

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome EntradaFunc.vwf.

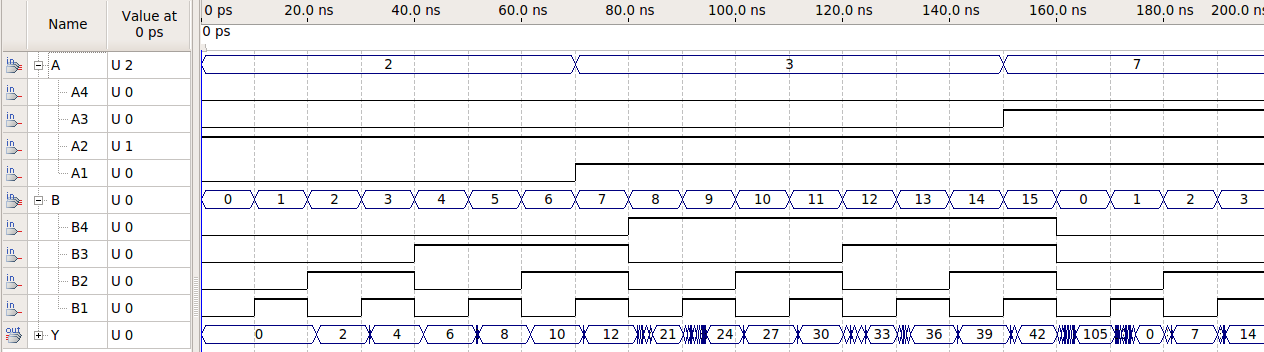

Fazer a simulação temporal do circuito com o QSIM

- Faça a simulação temporal do circuito e verifique o resultado obtido do circuito implementado.

- Através do uso de cursores, meça os atrasos de propagação apresentados no circuito.

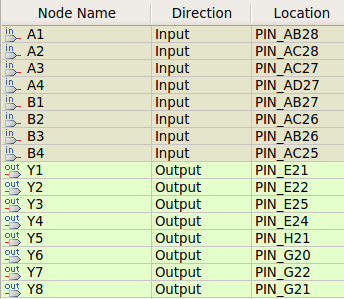

Preparar o circuito lógico para gravação em um kit de desenvolvimento

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2-115.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE22F17C7N

- Faça uma nova Análise e Sintese (Processing > Start > Start Analysis & Synthesis) para trocar de Device

- Abra o Pin Planner (Assignments > Pin_Planner) e atribua os pinos conforme a pinagem do kit DE2-115.

Kamila, aqui estava errado: precisas corrigir nos outros se tiver o mesmo erro. EP4CE22F17C6N e faltou também indicar: * Faça uma nova Análise e Sintese (Processing > Start > Start Analysis & Synthesis) para trocar de Device * Abra o Pin Planner (Assignments > Pin_Planner) --Marcos Moecke 10h57min de 6 de outubro de 2015 (BRT)

- Atribua os pinos conforme a pinagem do kit DE2-115.

- Utilize os leds verdes para indicar a saída.

- Utilize os switches para indicar as entradas.

- Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem:

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto e verifique se os pinos também aparecem no diagrama esquemático.

- No Quartus vá em (Tools > Programmer) para abrir a página de programação;

- Selecione o Hardware (Hardware Setup > USB-Blaster);

- Utilize o modo JTAG e clique em Start para começar a programação;

- Verifique os resultados obtidos.