Mudanças entre as edições de "DLP29006-Engtelecom(2015-1) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 651: | Linha 651: | ||

*Resolva os exercícios da capítulo 9 (1-3, 6-9) pag. 238 a 239. | *Resolva os exercícios da capítulo 9 (1-3, 6-9) pag. 238 a 239. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | |||

| + | ==Referências Bibliográficas:== | ||

| + | <references/> | ||

| + | |||

| + | |||

| + | {{ENGTELECO}} | ||

Edição das 09h37min de 29 de julho de 2015

Registro on-line das aulas

Unidade 1

- Aula 1 (5 fev)

- Dispositivos lógicos programáveis.

- Bases da linguagem VHDL.

- Tipos de dados, libraries, conversão de tipos, operadores, atributos.

- Código VHDL concorrente e sequencial.

- Projeto hierárquico.

- Simulação e Testbench

- Maquina de estado finita (FSM).

- Projeto Final de circuitos lógicos.

- Avaliações.

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD: PAL, PLA e GAL

- Ver pag. 413 a 418 de [1]

- Aula 2 (6 fev)

- Introdução aos dispositivos lógicos programáveis:

- CPLDs e FPGAs

- Fabricantes de DLPs

- Vizualização no Chip Planner de um projeto.

- Ver pag. 419 a 424 de [1]

- Aula 3 (11 fev)

- Introdução aos dispositivos lógicos programáveis:

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Vizualização no Chip Planner de um projeto.

- Ver pag. 424 a 431 de [1]

Unidade 2

- Aula 4 (12 fev)

- Introdução ao VHDL.

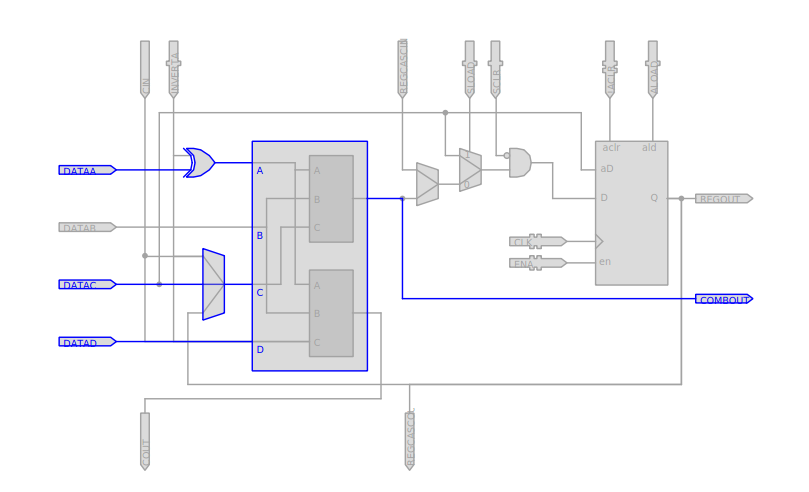

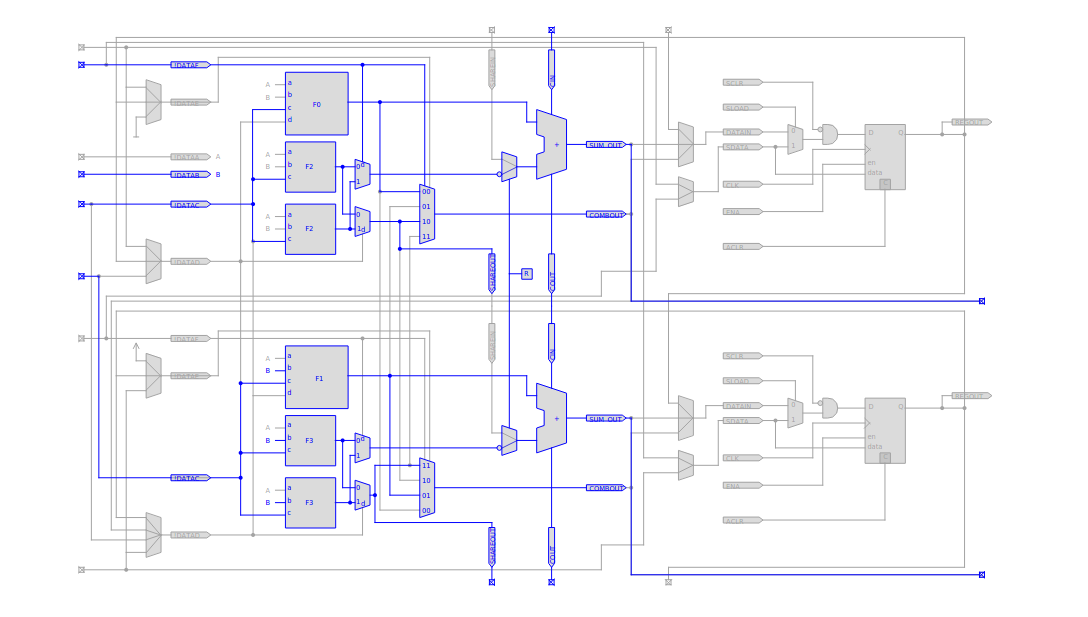

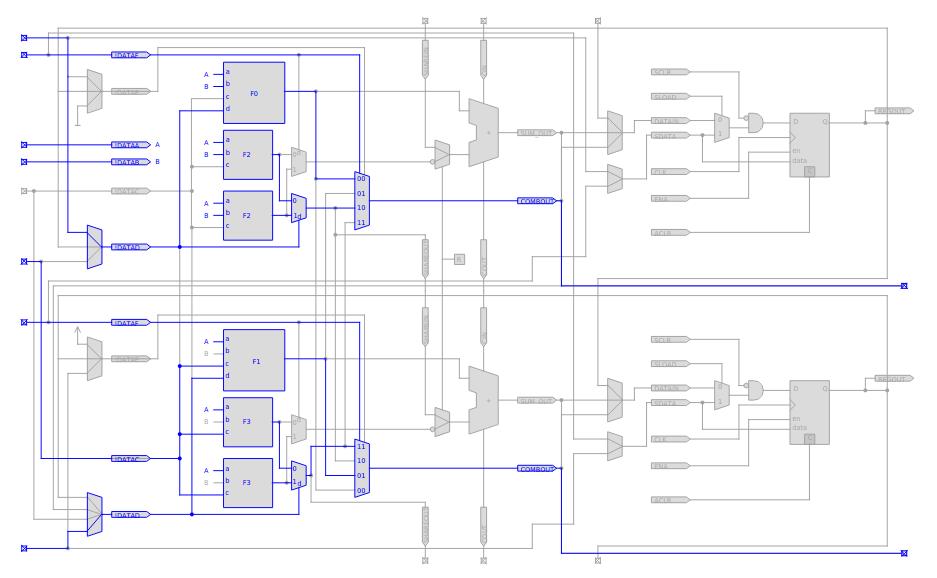

- Exemplo de programação de um full adder. Utilize os arquivos .qar enviados (V1 - estrutural. V2 - comportamental) para analisar os circuitos obtidos e realizar as simulações funcional e temporal.

- Ver pag. 3 a 8 de [2]

- Aula 5 (13 fev)

- Introdução ao VHDL.

- Estrutura do código VHDL

- Libraries, Entity, Architecture

- Aula 6 (19 fev)

- Introdução ao VHDL.

- Estrutura do código VHDL

- Exercicios 2.2 (VHDL e QSIM)

- Exemplo de programação de um flip-flop

- Exercicios 2.3 (VHDL e QSIM)

- Ver pag. 3 a 8 de [2]

- Aula 7 (20 fev)

- Introdução ao VHDL.

- Libraries, Entity, Architechture, Generic.

- Ver pag. 11 a 18 de [2]

- Aula 8 (25 fev)

- Introdução ao VHDL.

- Exemplo de um circuito somador

- Exemplo de FF-D

- Ver pag. 19 a 21 de [2]

Unidade 3

- Aula 9 (26 fev)

- Tipos de Dados em VHDL.

- Exemplo de um circuito somador com registrador

- Exemplo de decodificador de endereço genérico

- Ver pag. 22 a 27 de [2]

- Aula 10 (27 fev)

- Tipos de Dados em VHDL.

- Objetos de VHDL: CONSTANT, SIGNAL, VARIABLE, FILE.

- Palavra chave OTHERS

- Bibliotecas padrão.

- Não use as bibliotecas não padrão (std_logic_arith, std_logic_unsigned, std_logic_signed)

- Tipos de dados: BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING, STD_(U)LOGIG, STD_(U)LOGIG_VECTOR, (UN)SIGNED

- Classificação dos tipos de dados.

- Exemplo 3.1 Buffer Tri-state

- Exemplo 3.3 Multiplicador

- Ver pag. 31 a 54 de [2]

- Aula 11 (5 mar)

- Tipos de Dados em VHDL.

- Tipos Array definidos pelo usuário: 1D, 1D x 1D, 2D, 1D x 1D x 1D, 3D.

- Ver pag. 62 a 79 de [2]

- Aula 12 (6 mar)

- Operadores em VHDL.

- Operadores predefinidos: Atribuição, Logicos, Arithméticos, Comparação, Deslocamento, Concatenação, "Matching".

- Sobrecarga de operadores

- Ver pag. 91 a 98 de [2]

- Aula 13 (11 mar)

- Atributos em VHDL.

- Atributos predefinidos: tipo escalar e enumerados; tipo array; de sinal;

- Exemplo 4.1 (Simulação funcional)

- Atributos definidos pelo usuário;

- Atributos de síntese: Enum_encoding, chip_pin, keep.

- Exemplo: Delay line (Síntese e Simulação temporal sem o com o atributo keep)

- Ver pag. 99 a 109 de [2]

- Aula 14 (12 mar)

- Atributos em VHDL.

- Atributos de síntese: preserve, noprune.

- Exemplo: Redundant Register

- Group e Alias

- Exercício 4.17: Discussão de possibilidades de implementação

- Ver pag. 109 a 119 de [2]

Unidade 4

- Aula 15 (13 mar)

- Código Concorrente.

- WHEN, SELECT, GENERATE;

- Exemplo 5.1 + 5.2 mux: com 4 tipos de arquiteturas (com operadores, com WHEN, com SELECT, com IF),

- Uso de CONFIGURATION para selecionar um entre várias arquiteturas.

CONFIGURATION which_mux OF mux IS

FOR with_OPERATOR END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

-- FOR with_IF END FOR;

END CONFIGURATION;

- Exemplo 5.3 ALU: modificação do opcodes: "0011" -> a NAND b, "0100" -> "a OR b, "1111" => a * b. É necessário mudar a ENTITY, dobrando o número de bits da saída devido a multiplicação, e adaptar o código para a nova quantidade de bits.

- Ver pag. 121 a 129 de [2]

- Aula 16 (19 mar)

- Código Concorrente.

- Aula 17 (20 mar)

- Código Concorrente.

- Aula 18 (25 mar)

- Código Concorrente.

- Implementação de circuitos arithméticos com operadores.

- LEMBRETE

- Para "+" ou "-": O tamanho do resultado é igual ao número de bits do maior operando.

- r[7..0] = a[7..0] + b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8 bits.

- Para "*": O tamanho do resultado é igual a soma do número de bits dos dois operandos.

- r[12..0] = a[7..0] * b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8+5 bits.

- Para "/": O tamanho do resultado é igual ao número de bits do numerador.

- r[5..0] = a[5..0] * b[8..0]; a -> 6 bits; b -> 9 bits então r -> 6 bits.

- Aula de exercicios:

- 5.4 - Generic Parity Generator;

- 5.6 - Generic Binary-to-Gray Converter;

- 5.7 - Hamming Weight with GENERATE;

- 5.8 - Binary Sorter with GENERATE;

- 5.10/11 - Arithmetic Circuit with INTEGER/STD_LOGIC;

- 5.15/16/17/18 - (Un)signed Multiplier/Divider;

- 5.19 - Frequency Multiplier.

Unidade 5

- Aula 19 (26 mar)

- Código Sequencial.

- Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial

- Diferenças entre os objetos SIGNAL e VARIABLE

- Tipos de elementos de memória: Latch x Flip-flop

- Latch D

- Flip-flop tipo D com reset assíncrono e com reset (clear) síncrono

- Seção de código sequencial PROCESS: lista de sensibilidade

- Instrução IF

- Exemplos: DFFs with Reset and Clear (Variação Ex 6.1), Basic Counter (Ex. 6.2), Shift Register (Ex. 6.3)

- Instrução WAIT: WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II).

- Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT.

- Ver pag. 161 a 160 de [2]

- Aula 20 (27 mar)

- Código Sequencial.

- Instruções do tipo LOOP: LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT

- Exemplos: Carry-Ripple Adder (FOR-LOOP) (Ex 6.4), Leading Zeros (LOOP com EXIT) (Ex 6.5)

- Instrução CASE

- Exemplo: Contador de 0 a 9 segundos com saída SSD (Ex 6.6)

- Exemplo: Projeto ruim com CASE incompleto (Ex. 6.7)

- Ver pag. 161 a 171 de [2]

Unidade 6

- Aula 21 (8 abr)

- Projeto a nível de Sistema.

- O PACKAGE e PACKAGE BODY: onde declarar e como usar.

- O COMPONENT: declaração (cópia da ENTITY) e instanciação.

- Associação dos nomes das portas aos sinais. PORT -> PORT MAP:

- Ver pag. 201 a 205 de [2]

- Aula 22 (9 abr)

- Projeto a nível de Sistema.

- O COMPONENT:

- Criação de compomentes redimensionáveis. GENERIC -> GENERIC MAP

- Mapeamento por posição e nominal.

- Métodos de declaração de COMPONENT.

- Exemplo: Registrador Circular Ex. 8.2

- Ver pag. 205 a 208 de [2]

- Aula 23 (10 abr)

- Avaliação das Unidades 1 a 4.

- Aula 24 (16 abr)

- Projeto a nível de Sistema.

- Criação de COMPONENT redimensionáveis. GENERIC -> GENERIC MAP

- Exemplo: Porta E com N entradas.

- Exemplo: Detector de Paridade Ex. 8.3

- Instanciação de COMPONENT com GENERATE.

- Exemplo: Registrador de deslocamento M x N Ex. 8.4

- Ver pag. 208 a 213 de [2]

- Aula 25 (17 abr)

- Projeto a nível de Sistema.

- Uso da instrução CONFIGURATION.

- Ligação direta: ARCHITECTURE-ENTITY.

- Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE).

- O BLOCK.

- A instrução ASSERT condicional e incondicional

- A FUNCTION: declaração, uso, mapeamento posicional x nominal, PURE x IMPURE.

- Ver pag. 213 a 226 de [2])

- Ver exercício proposto na AE5.

- Aula 26 (22 abr)

- Projeto a nível de Sistema.

- Uso de FUNCTION e ASSERT.

- Exemplo: Declaração em ARCHITECTURE Ex.9.1

- Exemplo: Declaração em PACKAGE Ex. 9.2

- Exemplo: Declaração em ENTITY Ex. 9.3

- Ver pag. 226 a 230 de [2]

- Aula 27 (23 abr)

- Projeto a nível de Sistema.

- Uso de PROCEDURE.

- Exemplo: min_max Ex.9.4

- Exercícios: 9.1 a 9.4, 9.6 a 9.9

- Ver pag. 230 a 239 de [2]

- Aula 28 (24 abr)

- Projeto a nível de Sistema.

- Projeto de um conversor de hexadecimal para display de 7 segmentos.

- Ver EL7 - Projetar Conversor de hexadecimal para 7 segmentos

- Aula 29 e 30 (30 abr e 6 mai)

- Projeto a nível de Sistema.

- Projeto de um relógio com saída em display de 7 segmentos de HH:MM:SS.

- Ver EL8 - Projetar um relógio de 24 horas

Unidade 7

- Aula 31 (7 mai)

- Simulação com o ModelSim

- Seguir o tutorial [1]

- Para usar o ModelSim 10.1d na CLOUD-IFSC abra um terminal e digite:

/opt/altera/13.0sp1/modelsim_ase/bin/vsim

- Para usar o ModelSim 10.1d no LabProg abra um terminal e digite:

/opt/altera/13.0/quartus/modelsim_ase/linux/vsim

- Complementos

- Aula 32-33 (8 e 14 mai)

- Simulação com o ModelSim X Qsim

- Implementar o relógio da AE8 e realizar a simulação no QSIM e ModelSim.

- Executar Modelsim a partir do Quartus II. Simulação usando comandos gráficos.

- Criação de arquivo wave.do (para armazenamento dos sinais e formatos).

- Criação do arquivo tb_relógio.do (para compilar, simular, definir os estimulos e executar 48 hr de simulação).

- Análise dos graficos temporais e correção do hardware implementado.

- Aula 34 (15 mai)

-

- Tipos de testbench funcional e temporal:

- Gráfico -> DUT -> Gráfico (funcional RTL). Usar project.vhd + tp_project.vwf (QSIM) ou project.vhd + tb_project.do (ModelSim)

- Gráfico -> DUT -> Gráfico (funcional pós-síntese). Usar project.vho + tb_project.do (ModelSim)

- Geração de estimulos para testbench:

- VHDL -> DUT -> Gráfico (funcional RTL). Usar project.vhd + tp_project.vwf (QSIM) ou project.vhd + tb_project.vhd (ModelSim)

- VHDL -> DUT -> Gráfico (funcional pós-síntese). Usar project.vho + tb_project.vhd (ModelSim)

- VHDL -> DUT -> Gráfico (temporal). Usar project.vho + tb_project.vhd + project.sdo (ModelSim)

- Teste automático da saída usando o sinal esperado e tempo de propagação.

- VHDL -> DUT -> VHDL (funcional RTL). Usar project.vhd + tp_project.vwf (QSIM) ou project.vhd + tb_project.vhd (ModelSim)

- VHDL -> DUT -> VHDL (funcional pós-síntese). Usar project.vho + tb_project.vhd (ModelSim)

- VHDL -> DUT -> VHDL (temporal). Usar project.vho + tb_project.vhd + project.sdo (ModelSim)

- Exemplo Multiplexador Registrado

- Ver pag. 241 a 245 e 251 a 264 de [2]

- Complementos

-

- Ver também site que gera um template de testbench a partir do código vhdl da top_entity (DUT): http://www.doulos.com/knowhow/perl/testbench_creation/

- Ver este tutorial da ALTERA que ensina como gerar um template de testbench usando o Quartus II.

- Aula 35 (20 mai)

-

- Simulação do RelógioHHMMSS da AE6 no ModelSim tanto funcional como temporal

- teste com geração automática de estimulo (clk) com VHDL -> DUT -> Gráfico.

- teste com análise automática das saídas VHDL -> DUT -> VHDL.

Unidade 8

- Aula 36 (21 mai)

- Máquinas de Estados Finitos (FSM)

- Diagrama de transições, Representação em Hardware

- Template VHDL para FSM, exemplo 11.1 "vending_machine"

- Simulação do Ex11.1 no Modelsim com testbench de geração de estímulos em VHDL.

- Ver pag 277 a 287 de [2]

- Aula 37 (22 mai)

- Dúvida sobre o Exercício 6.9 (debouncer)

- Máquinas de Estados Finitos (FSM)

- Simulação funcional e temporal do Ex11.3 no Modelsim com testbench de geração de estímulos em VHDL.

- Criando projeto no ModelSim para facilitar a simulação.

- Ver pag 287 de [2]

- Aula 38 (28 mai)

- Dúvida sobre os Exercícios da Unidade 5 e 6

- Termino do testbench do Projeto do relógio HH:MM:SS.

- Aula 39 (29 mai) (2h30)

- Avaliação A2

- Aula 40 (4 jun)

- Máquinas de Estados Finitos (FSM)

- Tipos de codificação dos estados: Sequential, Gray, Johnson, One-hot, "User-defined encoding".

--------------------------------------------------------

TYPE state IS (A, B, C, D, E, F);

SIGNAL pr_state, nx_state: state;

--------------------------------------------------------

ATTRIBUTE enum_encoding: STRING;

ATTRIBUTE enum_encoding OF state: TYPE IS "sequential";

-- A="000", B="001", C="010", D="011", E="100", F="101"

--------------------------------------------------------

ATTRIBUTE enum_encoding: STRING;

ATTRIBUTE enum_encoding OF state: TYPE IS "gray";

-- A="000", B="001", C="011", D="010", E="110", F="111"

--------------------------------------------------------

ATTRIBUTE enum_encoding: STRING;

ATTRIBUTE enum_encoding OF state: TYPE IS "johnson";

-- A="000", B="100", C="110", D="111", E="011", F="001"

--------------------------------------------------------

ATTRIBUTE enum_encoding: STRING;

ATTRIBUTE enum_encoding OF state: TYPE IS "one-hot";

-- A="000001", B="000010", C="000100", D="001000", E="010000", F="100000"

--------------------------------------------------------

ATTRIBUTE enum_encoding: STRING;

ATTRIBUTE enum_encoding OF state: TYPE IS "111 100 110 011 000 101";

-- A="111", B="100", C="110", D="011", E="000", F="101"

--------------------------------------------------------

- Detalhes de uso do Quartus II para definir o tipo de codificação dos estados.

- Se não for usado o ATTRIBUTE enum_encoding, é possível definir diretamente no quartus o tipo de enumeração a ser usado na maquina de estado.

- Para selecionar o tipo [Assignments > Settings > Analysis & Synthesis Settings > More Settings > State Machine Processing > [Escolha a opção]].

- Resolvendo o problema do Bypass de estados com Flags e estados de Wait.

- Simulação funcional do Ex11.4 e 11.5 no Modelsim com testbench de geração de estímulos em VHDL.

- Ver pag 289 a 297 de [2]

Unidade 9

- Aula 41 a 50 (11/06 a 3/06)

Projeto, Simulação e Implementação de um sistema.

- Os alunos foram divididos em equipes de 2 alunos, e cada equipe projetou, simulou e implementou um sistema.

- EQUIPE 1: Matuzalem.

- EQUIPE 2: Tiago.

- EQUIPE 3: Karoline e Ana.

- EQUIPE 4: Guilherme e Mathias.

- Ao final do projeto, além do código VHDL e das simulações e teste utilizando um kit FPGA, cada equipe de apresentar um relatório com a descrição detalhada do projeto e os resultados obtidos.

Avaliações

- Avaliação A1 - Unidade 2, 3 e 4

- Avaliação A2 - Unidade 5 e 6

- Entrega dos diversos trabalhos ao longo do semestre AE1 a AE7.

- Projeto Final. Tem peso equivalente a duas avaliações, sendo avaliado nos quesitos: 1) Implementação do Sistema, 2) Documentação, 3) Avaliação Global do aluno no projeto.

Atividades extra

JÁ ENCERRADAS

| AE1 - Estudo do tipo de programação dos FPGA (prazo 20/02/2015) |

|---|

|

| AE2 - Estudo do Quartus II e Dispositivos FPGA (prazo 27/02/2015) |

|---|

|

| AE3 - Uso de operadores e tipos de dados (Prazo de entrega 23/03/2015) |

|---|

entity bin2bcd is

port (

num_bin : in std_logic_vector(9 downto 0);

C_bcd : out std_logic_vector(3 downto 0);

D_bcd : out std_logic_vector(3 downto 0);

U_bcd : out std_logic_vector(3 downto 0));

end entity;

|

| AE4 - Uso de código concorrente - ALU multiplicadora (Prazo de entrega 01/04/2015) | ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

ENTITY alu IS

GENERIC (N: INTEGER := 4); --word bits

PORT (

a, b: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

opcode: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

valid: out STD_LOGIC;

y: OUT STD_LOGIC_VECTOR(2*N-1 DOWNTO 0));

END ENTITY;

|

| AE5 - Circuitos Genéricos com código estrutural (Prazo de entrega 04/05/2015) |

|---|

|

| AE6 - Testbench completo para FSM do alarme do carro(Prazo de entrega 11/06/2015) |

|---|

|

| AE7 - Simulação e Teste Final do Relógio HH:MM:SS (Prazo de entrega 17/06/2015) |

|---|

|

| Projeto Final (Prazo de entrega 06/07/2015) |

|---|

|

ESTUDOS LIVRES (DE DOCUMENTAÇÃO)

| EL1 - Estrutura do VHDL |

|---|

|

| EL2 - Estudo dos atributos em VDHL |

|---|

entity atributte_test_array is

port(

x1, x2, x3, x4, x5, x6: out integer range 0 to 15;

x7, x8: out boolean;

m12, m44, m47: out bit);

end entity;

architecture ifsc of atributte_test_array is

TYPE matrix IS ARRAY (1 TO 4, 7 DOWNTO 0) OF BIT;

SIGNAL test: matrix := (('0', '1', '1', '0', '0', '1', '1', '0'), "01110100", ('1', others => '0'), (4 => '0', others => '1'));

begin

--------------------------------------------------------------------------

x1 <= matrix'LEFT(1); --result=1 (type of x1 must be INTEGER or eq.)

x2 <= matrix'LEFT(2); --result=7 (type of x2 must be INTEGER or eq.)

x3 <= matrix'RIGHT(1); --result=4 (type of x3 must be INTEGER or eq.)

x4 <= matrix'RIGHT(2); --result=0 (type of x4 must be INTEGER or eq.)

x5 <= matrix'LENGTH(1); --result=4 (type of x5 must be INTEGER or eq.)

x6 <= matrix'LENGTH(2); --result=8 (type of x6 must be INTEGER or eq.)

x7 <= matrix'ASCENDING(1); --result=TRUE (type of x7 must be BOOLEAN)

x8 <= matrix'ASCENDING(2); --result=FALSE (type of x8 must be BOOLEAN)

m12 <= test(1,2); -- result = '1' - Acess the element of 'test' row(1), columm(2) (type of m11 must be bit)

m47 <= test(4,7); -- result = '1' - Acess the element of 'test' row(7), columm(7) (type of m11 must be bit)

m44 <= test(4,4); -- result = '0' - Acess the element of 'test' row(4), columm(4) (type of m11 must be bit)

--------------------------------------------------------------------------

end architecture;

|

| EL3 - Resolução dos exercícios do Cap 3 |

|---|

|

| EL4 - Resolução dos exercícios do Cap 4 |

|---|

|

| EL5 - Resolução dos exercícios do Cap 5 |

|---|

|

| EL6 - Projetar Conversor de binário para 7 segmentos |

|---|

|

Projetar em VHDL dois conversores de binário para 7 segmentos a) usando código concorrente (SELECT) e b) usando código sequencial (CASE).

ENTITY ssd IS

PORT (

bin: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ssd: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END ENTITY;

|

| EL7 - Projetar Conversor de hexadecimal para 7 segmentos |

|---|

Use como top-entity: ENTITY hex2ssd IS

PORT (

hex: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ssd: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END ENTITY;

|

| EL8 - Projetar um relógio de 24 horas |

|---|

entity relogio_HHMMSS is

port

(

rst : in std_logic; -- Reset assincrono do relogio

clk_1seg : in std_logic; -- Sinal de clock com periodo de 1 segundo

SS_U, SS_D : out std_logic_vector(6 downto 0); -- Saida ssd de Unidade e Dezena de Segundo

MM_U, MM_D : out std_logic_vector(6 downto 0); -- Saida ssd de Unidade e Dezena de Minuto

HH_U, HH_D : out std_logic_vector(6 downto 0) -- Saida ssd de Unidade e Dezena de Hora

);

end entity;

|

| EL9 - Resolução dos exercícios do Cap 6, 8 e 9 |

|---|

|

Referências Bibliográficas:

- ↑ 1,0 1,1 1,2 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 2,14 2,15 2,16 2,17 2,18 2,19 2,20 2,21 2,22 2,23 2,24 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335