Mudanças entre as edições de "ELD129002-Engtelecom (Diário) - Prof. Marcos Moecke"

(→ATUAL) |

|||

| (18 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 1 402: | Linha 1 402: | ||

*Ler a seção '''2.7.MAPAS DE KARNAUGH''' nas pag 99 a 108 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=125 Projeto Digital e Arquitetura de Computadores] | *Ler a seção '''2.7.MAPAS DE KARNAUGH''' nas pag 99 a 108 de [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=125 Projeto Digital e Arquitetura de Computadores] | ||

| − | + | ||

| − | ;Encontro 15 ( | + | ;Encontro 15 (9 abr.) - Projeto de circuitos combinacionais: |

| − | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/ | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311789/mod_resource/content/1/Projeto%20de%20circuitos%20combinacionais.pdf Projeto de circuitos combinacionais] |

*Multiplexadores e Decodificadores: | *Multiplexadores e Decodificadores: | ||

*Ler a seção '''2.8.BLOCOS COMBINATÓRIOS''' nas pag 109 a 114 [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=135 Projeto Digital e Arquitetura de Computadores] | *Ler a seção '''2.8.BLOCOS COMBINATÓRIOS''' nas pag 109 a 114 [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=135 Projeto Digital e Arquitetura de Computadores] | ||

| − | *Exercícios 2.1, 2.2, 2.5-7, 2.13-18 | + | |

| + | ;Encontro 16 (11 abr.) | ||

| + | *Exercícios 2.1, 2.2, 2.5-7, 2.13-18, 2.22-25, 2.28-29, 2.31-32, 2.34, 2.35, 2.36-37, 2.39-40 ver [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=151] | ||

| + | *Pergunta 2.2, 2.3, 2.4 ver [https://moodle.ifsc.edu.br/pluginfile.php/311785/mod_resource/content/1/DDCA_portugues.pdf#page=163] | ||

| + | |||

| + | ;Encontro 18 (23 abr.) - Avaliação A1c (6 pontos): | ||

| + | *Simplificação de expressões lógicas e mapa de Karnaugh | ||

| + | *Representação de circuitos lógicos - '''Diagrama de portas lógicos = Tabela Verdade = Expressão lógica''' | ||

<!-- | <!-- | ||

| Linha 1 434: | Linha 1 441: | ||

* 6 ENCONTROS | * 6 ENCONTROS | ||

{{collapse top | expand=true |Unidade 4 - Introdução a linguagem VHDL e Quartus/ModelSim }} | {{collapse top | expand=true |Unidade 4 - Introdução a linguagem VHDL e Quartus/ModelSim }} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | ;Encontro 18 | + | ;Encontro 17 (18 abr.) - Linguagem VHDL: |

| − | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/ | + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311793/mod_resource/content/2/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] |

| + | |||

| + | ====ATUAL==== | ||

| + | ;Encontro 19 (25 abr.) - Linguagem VHDL: | ||

| + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/311793/mod_resource/content/2/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] | ||

* Estrutura do código VHDL | * Estrutura do código VHDL | ||

| Linha 1 536: | Linha 1 542: | ||

;PASSO 5: | ;PASSO 5: | ||

*Modifique a descrição do circuito para implementar o circuito da função Y = (A.B)' + C.D'B', salve o projeto Ckt2.vhd e de o mesmo nome para a entity. | *Modifique a descrição do circuito para implementar o circuito da função Y = (A.B)' + C.D'B', salve o projeto Ckt2.vhd e de o mesmo nome para a entity. | ||

| + | |||

| + | ;PARA O PRÓXIMO ENCONTRO | ||

| + | *Escreva em VHDL o circuito do [https://wiki.sj.ifsc.edu.br/index.php/ELD129002-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE1_-_Projeto_de_um_conversor_de_bin.C3.A1rio_para_mostrador_de_7_segmentos AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos] | ||

| + | :*Use como modelo: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- A bibliteca std e o pacote standard são autodeclarados, então as linhas abaixo podem ser comentadas com "--" | ||

| + | --library std; | ||

| + | --use std.standard.all; | ||

| + | |||

| + | entity BCD2SSD is | ||

| + | port ( | ||

| + | -- Entradas ABCD do circuito | ||

| + | A, B, C, D: in bit; | ||

| + | -- Saidas para os leds do mostrador de 7 segmentos. Note que o nome a, b, .. g foi mudado para ssd_a, ssd_b, ... ssd_g pois o VHDL é insensível a caixa | ||

| + | ssd_a, ssd_b, ssd_c, ssd_d, ssd_e, ssd_f, ssd_g : out bit | ||

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc_v1 of BCD2SSD is | ||

| + | begin | ||

| + | -- descreva a expressão lógica obtida para cada uma das saídas; | ||

| + | -- Por exemplo: se for a = A + C + (B'.D') + (B.D) | ||

| + | ssd_a <= A or C or (not B and not D) or (B and D); | ||

| + | |||

| + | ssd_g <= ; | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Ler [https://pt.wikipedia.org/wiki/VHDL VHDL] na Wikipedia. | ||

| + | *Guardar [[Folha de consulta de VHDL]] | ||

| + | |||

| + | <!-- | ||

| + | ;Encontro 18 (18 abr.) - Avaliação A1c (6 pontos): | ||

| + | *Simplificação de expressões lógicas e mapa de Karnaugh | ||

| + | *Representação de circuitos lógicos - '''Diagrama de portas lógicos = Tabela Verdade = Expressão lógica''' | ||

| + | |||

| + | ;Encontro 18 (28 set) - Linguagem VHDL (cont): | ||

| + | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/262427/mod_resource/content/1/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] | ||

| + | |||

;Encontro 19 (3 out.) - Simulador ModelSim: | ;Encontro 19 (3 out.) - Simulador ModelSim: | ||

| Linha 2 633: | Linha 2 678: | ||

:3) Para cada saída deve ser apresentada a expressão lógica minimizada e também o circuito lógico obtido. | :3) Para cada saída deve ser apresentada a expressão lógica minimizada e também o circuito lógico obtido. | ||

*A entrega será feita pessoalmente para o professor no prazo indicado no Moodle. | *A entrega será feita pessoalmente para o professor no prazo indicado no Moodle. | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===AE2 - Conhecendo os dispositivos lógicos programáveis=== | ||

| + | {{collapse top | bg=lightyellow | AE2 - Conhecendo os dispositivos lógicos programáveis}} | ||

| + | ;Objetivos: | ||

| + | *Conhecer o Quartus Prime e as características dos dispositivos lógicos programáveis | ||

| + | *Analisar os tempos de propagação em um circuito combinacional | ||

| + | *Alterar configurações do compilador | ||

| + | *Fazer a simulação funcional de um circuito combinacional. | ||

| + | |||

| + | ;Atividades: | ||

| + | *'''PASSO 1:''' Realize a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis - QUARTUS PRIME]] | ||

| + | :*Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família '''Max II'''. Anote o código desse dispositivo. | ||

| + | :*Capture as telas solicitadas e depois utilize-as no relatório da atividade. | ||

| + | :*Anote o tempo utilizado para cada uma das etapas do processo de compilação. | ||

| + | :*Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo. | ||

| + | :*Anote algum erro ('''Error''') ou alertas ('''Warnings''') que o Quartus II indicar no painel de mensagens '''[Messages]''' | ||

| + | :*Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR) | ||

| + | |||

| + | *'''PASSO 2''': Repita a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis - QUARTUS PRIME]], trocando a família e dispositivo a ser usado na implementação. Escolha nesta vez um dispositivos da família '''Cyclone IV E''' ou '''Stratix II GX'''. Anote o código desse dispositivo. | ||

| + | :*Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar. | ||

| + | :*Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2. | ||

| + | |||

| + | *'''PASSO 3''': Realize o procedimento descrito em [[Medição de tempos de propagação em circuitos combinacionais - Quartus Prime]] | ||

| + | :*Ao escolher a família de FPGAS, escolha um dispositivo FPGA da família '''Cyclone IV E'''. Anote o código desse dispositivo. | ||

| + | :*Se você está com o código da '''AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos''' escrito, use este código no lugar do código do '''cálculo da distância de Hamming''' | ||

| + | :*Capture as telas mostradas no roteiro e depois utilize-as no relatório da atividade. | ||

| + | :*Anote o máximo tempo de propagação entre entrada e saída. | ||

| + | :*Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo. | ||

| + | :*Experimente modificar as configurações do compilador, conforme mostrado em '''Configurando o compilador'''. Se desejar mude a semente inicial trocando o valor de '''[Seed: 1]''' | ||

| + | :*Experimente inserir diferentes restrições de atraso máximo para o compilador, e analise o resultado obtido. | ||

| + | :*Anote algum erro ('''Error''') ou alertas ('''Warnings''') que o Quartus II indicar no painel de mensagens '''[Messages]''' | ||

| + | :*Ao final salve o projeto em um arquivo QAR (sugestão PJ2.QAR) | ||

| + | |||

| + | *'''PASSO 4''': Realize a simulação funcional de um dos projetos '''CI74161''' ou do '''cálculo da distância de Hamming''' ou '''conversor de binário para mostrador de 7 segmentos''' | ||

| + | :*Capture as telas que mostram o circuito funcionando e depois utilize-as no relatório da atividade. | ||

| + | |||

| + | ;Entregas: | ||

| + | #Envie um arquivo QAR contendo todos os arquivos necessário para compilar cada um dos projetos. | ||

| + | #Envie um relatório em PDF, incluindo as imagens capturadas (inclua um título para cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório. | ||

| + | #Use preferencialmente o [[Uso_do_Overleaf | Overleaf]] para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida. | ||

| + | #A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega. | ||

| + | {{collapse bottom}} | ||

| + | <!-- | ||

| + | |||

| + | ===AE3 - Implementação do conversor de binário para mostrador de 7 segmentos === | ||

| + | {{collapse top | bg=lightyellow | AE3 - Implementação do conversor de binário para mostrador de 7 segmentos}} | ||

| + | ;Objetivos: | ||

| + | * Baseado na '''AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos''', implementar o projeto em VHDL. | ||

| + | * Descrever um circuito que você projetou em VHDL, implentá-lo e testá-lo. | ||

| + | |||

| + | ;Atividades: | ||

| + | * Rever atividade '''AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos''' | ||

| + | * Baseado no código VHDL da nand_gate. | ||

| + | * Descrever em código VHDL as expressões lógicas obtidas em AE1. | ||

| + | * Realizar no Quartus a Análise e Síntese do projeto, verificar o RTL viewer e Technology map. | ||

| + | * Realizar a simulação no ModelSim. | ||

| + | * Definir quais pinos do FPGA serão usados (chaves A, B, C, D) e os segmentos do mostrador (ssd_0 até ssd_7) | ||

| + | * Fazer os testes no kit '''DE2-115''' ou '''Mercúrio IV''' (conforme disponibilidade) | ||

| + | |||

| + | ;Entregas: | ||

| + | *O projeto todo deverá se realizado manuscrito, devendo as folhas ter a identificação do nome completo do estudante e estar grampeadas. *Deverão ser apresentados no mínimo: | ||

| + | :1) A tabela verdade completa indicando para as entradas de 0 a 9 quais são os valores das saídas (segmentos) a, b, c, d, e, f, g. | ||

| + | :2) Para cada saída mostre o mapa de Karnough e a indicação dos agrupamentos de bits obtidos, e o respectiva produto (implicante). | ||

| + | :3) Para cada saída deve ser apresentada a expressão lógica minimizada e também o circuito lógico obtido. | ||

| + | *A entrega será feita pessoalmente para o professor no prazo indicado no Moodle. | ||

| + | {{collapse bottom}} | ||

| + | --> | ||

==Referências Bibliográficas:== | ==Referências Bibliográficas:== | ||

<references/> | <references/> | ||

{{ENGTELECO}} | {{ENGTELECO}} | ||

Edição das 18h54min de 26 de abril de 2024

Registro on-line das aulas

Unidade 1 - Aula inicial, Introdução a disciplina

- 1 ENCONTRO

| Unidade 1 - Aula inicial, Introdução a disciplina |

|---|

|

Unidade 2 - Sistema de numeração e códigos

- 4 ENCONTROS

| Unidade 2 - Sistema de numeração e códigos | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

O ser humano precisa contar para determinar quantidades de coisas, com as quantidades ele pode fazer operações matemáticas e comparações.

O quadro abaixo mostra as representações em binário dos valores de +15 a -8 no sistema sem sinal (UNSIGNED), com signal-magnitude , com sinal em complemento de um , com sinal em complemento de dois (SIGNED). No quadro é importante notar que sempre os números negativos tem o msb = 1. Adicionalmente alguns sistemas possuem dois zeros (+0 e -0). No tipo SIGNED note que o valor máximo positivo será menor que o valor absoluto do mínimo negativo, por uma unidade.

13 (decimal) = 1101 (binário sem sinal) +13 (decimal) = 01101 (binário em sinal-magnitude) -13 (decimal) = 11101 (binário em sinal-magnitude) +13 (decimal) = 01101 (binário em complemento de um) -13 (decimal) = 10010 (binário em complemento de um) +13 (decimal) = 01101 (binário em complemento de dois) -13 (decimal) = 10011 = 10010 + 1 (binário em complemento de dois)

O código ASCII (American Standard Code for Information Interchange), é um padrão de codificação de caracteres para comunicação digital. Ele tem apenas 128 pontos de código, sendo 95 são caracteres imprimíveis e os demais são não imprimíveis (em azul no quadro abaixo), sendo usados para diversos controles de equipamentos eletrônicos. Atualmente esse código está sendo substituido pelos códigos UNICODE, que tem milhões de pontos de código, mas nos UNICODE os primeiros 128 são iguais ao conjunto ASCII.

Exemplo de leitura do quadro acima:

Descubra o que está escrito neste código binário onde cada 8 bits correspondem a um simbolo ASCII: 01000010 01101111 01101101 00100000 01100100 01101001 01100001 00100000 01110000 01100101 01110011 01110011 01101111 01000001 01001100 01001100

O Unicode é capaz de representar uma ampla variedade de caracteres, incluindo caracteres alfabéticos, numéricos, símbolos, caracteres especiais e até mesmo caracteres em idiomas e sistemas de escrita complexos, como chinês, árabe, hindi, hebraico, japonês, emojis entre outros. O Unicode possui um espaço de codificação grande o suficiente para suportar milhares de caracteres diferentes. O Unicode é implementado nos esquemas de codificação UTF-8, UTF-16 e UTF-32. O mais utilizado na web é o UTF-8, por ser eficiente em uso de número de bits e ser compatível com o ASCII. Hoje em dia o UTF-8 é usado em 98% de todos os websites conhecidos [1]. Para cobrir uma vasta gama de caracteres, o Unicode os organiza em blocos. Exemplos de blocos: "Latin basic","Greek and Coptic", "Chess Symbols", "Emoticons", "Mayan Numerals", etc.

Exemplo: Estender o número binário sem sinal de 5 bits "01101" para 8 bits: Número original: 01101 = (13 em decimal), pois 8 + 4 + 1 = 13 Número estendido: 00001101 = (13 em decimal), pois 8 + 4 + 1 = 13

Exemplo: Estender o número binário com sinal em complemento de 2 de 5 bits "10011" para 8 bits: Número original: 10011 = (-13 em decimal), pois -16 + 2 + 1 = -13 Número estendido: 11110011 = (-13 em decimal), pois -128 + 64 + 32 + 16 + 2 + 1 = -13

Exemplo: Estender o número binário com sinal em sinal-magnitude de 5 bits "10011" para 8 bits: Número original: 11101 = (-13 em decimal), pois -(+8 + 4 + 1) = -13 Número estendido: 10001101 = (-13 em decimal), pois -(+8 + 4 + 1) = -13

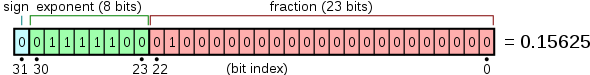

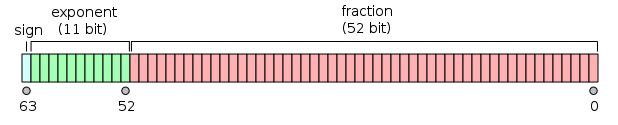

Embora o expoente possa ser positivo ou negativo, em formatos binários ele é armazenado como um número sem sinal que possui um "viés" fixo adicionado a ele. A faixa de expoente para números normais é [−126, 127] para precisão simples, [−1022, 1023] para dupla. Existem três tipos principais de números: normalizados, denormalizados (ou desnormalizados) e especiais (como infinito e NaN - "Not a Number"). Nos formatos IEEE, o bit 1 inicial de um significando normalizado não é realmente armazenado. É chamado de bit "oculto" ou "implícito". Por causa disso, o formato de precisão simples na verdade tem um significando com 24 bits de precisão, o formato de precisão dupla tem 53. O layout para o ponto flutuante de 32 bits e de 64 bits são mostrados abaixo:

Exemplo: Dado o número 85,125 converta para a representação floating point de 32 bits P1: 32 bits, portanto o viés é 127. P2: 85 em binário é 1010101. 0.125 em binário é 0.001. Portanto, 85,125 em binário é 1010101.001 P3: 1010101.001 => 1.010101001 × 2^6 P4: O número é positivo, então o bit de sinal é 0. O expoente é o deslocamento necessário para normalizar a mantissa. No caso, 6. A mantissa é a parte fracionária normalizada, que é 010101001.(note que o 1 a esquerda do ponto decimal não será representado. P5: Expoente = 6 + 127 = 133 em binário é 10000101. P6: Sinal: 0, Expoente: 10000101, Mantissa: 01010100100000000000000 (completar com zeros até 23 bits), portanto 0 10000101 01010100100000000000000

Exemplo: Dado o número representado em floating point de 32 bits = 11000000111000000000000000000000 P1: Expoente tem 8 bits => viés = 127 (28-1-1) P2: Sinal (msb): 1 => é um número negativo (-) P3: Expoente (8 bits): 10000001 = 129 P4: expoente (e = E - vies) 129 - 127 = 2 P5: Mantissa: (23 bits): 11000000000000000000000 P6: Valor (24 bits):1.11000000000000000000000 = 1,75 P7: Resultado: (-) 1,75 x 22 = -7

Os números sub_normais são indicados pelo Expoente = 00000000. Esse Expoente será interpretado como 2-126. Eles, ao contrário dos números normalizados, não usam um "1" implícito no início da mantissa. Isso significa que a mantissa desses números começa com um "0" explícito antes da parte fracionária, permitindo representar valores muito pequenos que não podem ser normalizados devido à limitação dos bits do expoente. Exemplos: 0 00000000 00000000000000000000000 corresponde ao número +0 1 00000000 00000000000000000000000 corresponde ao número -0 0 00000000 10000000000000000000000 corresponde ao número 0,5 x 2-126 = 5.877472E-39 1 00000000 00000000000000000000001 corresponde ao número -2-23 x 2-126 = -0.00000011920928955078125 x 2-126 = -1.40129846432481707092373E-45 (2-149

Mantissa: Todos os bits definidos como 0 (23 bits) Representação em 32 bits: 0 11111111 00000000000000000000000

Mantissa: Todos os bits definidos como 0 (23 bits) Representação em 32 bits: 1 11111111 00000000000000000000000

Mantissa: Pelo menos um bit não nulo (23 bits) Representação: x 11111111 yyyyyyyyyyyyyyyyyyyyyyy (onde "x" é o bit de sinal e "y" são bits da mantissa)

Unidade 3 - Funções, portas lógicas e álgebra booleana

Unidade 4 - Introdução a linguagem VHDL e Quartus/ModelSim

Unidade 5 - Circuitos lógicos combinacionais (com VHDL)

Unidade 6 - Circuitos aritméticos (com VHDL)

AvaliaçõesDurante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

Atividade relâmpago (AR)As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Atividade extra-classe (AE)A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE1 - Projeto de um conversor de binário para mostrador de 7 segmentos

AE2 - Conhecendo os dispositivos lógicos programáveis

Referências Bibliográficas:

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

![{\displaystyle [0,2^{N}-1]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/f5eb25a6a539bf3a9955017f5aba01160cdc022b)

![{\displaystyle [0,2^{8}-1]=[0,255]=[00000000_{2},11111111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/fb5be03ed649ead5e68cd72a508f2e35a85a9cd9)

![{\displaystyle [-(2^{N-1}-1),(2^{N-1}-1(]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/a221d72e8db48e0485fc9c806eddebf90d025d8b)

![{\displaystyle [-(2^{8-1}-1),(2^{8-1}-1)]=[-(2^{7}-1),(2^{7}-1)]=[-127,-0,+0,+127]=[11111111_{2},10000000_{2},00000000_{2},01111111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/3ee583c3440ece4c0754ca09cb58bcca0f94272f)

![{\displaystyle [-2^{N-1},2^{N-1}-1]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/98c77c4023c4f8693ba0abfb43664b86e21efda7)

![{\displaystyle [-2^{N-1},2^{N-1}-1]=[-128,0,+127]=[10000000_{2},00000000_{2},01111111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/09a57011cf81984fda5df4a154f54e5e84d6bb6a)

![{\displaystyle [0,2^{M-F}-2^{-F}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/031f01267eaa1c78218b276afbbbf48df80b6ea2)

![{\displaystyle [0;2^{5}-2^{-3}]=[0;31,875]=[00000,000_{2};11111,111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/7c35daa9c5e766f28942844286e64b06a889c510)