Mudanças entre as edições de "DLP29006-Engtelecom(2017-2) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 1: | Linha 1: | ||

{{DivulgueEngtelecom}} | {{DivulgueEngtelecom}} | ||

==Registro on-line das aulas== | ==Registro on-line das aulas== | ||

| − | + | {{collapse top| Unidade 1 - Inicialização}} | |

| − | {{collapse top| Unidade 1}} | + | ===Unidade 1 - Inicialização=== |

;Aula 1 (27 Jul): | ;Aula 1 (27 Jul): | ||

*[[DLP1-EngTel (Plano de Ensino) | Apresentação da disciplina]] | *[[DLP1-EngTel (Plano de Ensino) | Apresentação da disciplina]] | ||

| Linha 62: | Linha 62: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | {{collapse top| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} | |

| − | {{collapse top| Unidade 2}} | + | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== |

;Aula 4 (9 ago): | ;Aula 4 (9 ago): | ||

* Introdução ao VHDL e ambiente EDA - QUARTUS | * Introdução ao VHDL e ambiente EDA - QUARTUS | ||

| Linha 202: | Linha 202: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | {{collapse top| Unidade 3 - Tipos de Dados e Operadores em VHDL}} | |

| − | {{collapse top| Unidade 3}} | + | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== |

;Aula 6 (17 Ago): | ;Aula 6 (17 Ago): | ||

*Tipos de Dados em VHDL. | *Tipos de Dados em VHDL. | ||

| Linha 374: | Linha 374: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | {{collapse top| Unidade 4 - Código Concorrente}} | |

| − | {{collapse top| Unidade 4}} | + | ===Unidade 4 - Código Concorrente=== |

*Código Concorrente. | *Código Concorrente. | ||

:* Uso de Operadores | :* Uso de Operadores | ||

| Linha 489: | Linha 489: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | ===Unidade 5=== | + | {{collapse top| Unidade 5 - Código Sequencial}} |

| + | ===Unidade 5 - Código Sequencial=== | ||

;Aula 20 (17 Out): | ;Aula 20 (17 Out): | ||

*Realização da [https://moodle.sj.ifsc.edu.br/mod/forum/view.php?id=3639 SAD - Avaliação Docente pelos Discentes] | *Realização da [https://moodle.sj.ifsc.edu.br/mod/forum/view.php?id=3639 SAD - Avaliação Docente pelos Discentes] | ||

| Linha 632: | Linha 633: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

:::*Programe o FPGA usando o programador e verifique se a contagem está correta (a cada segundo). | :::*Programe o FPGA usando o programador e verifique se a contagem está correta (a cada segundo). | ||

| + | {{collapse bottom}} | ||

| − | + | {{collapse top| expand = true | Unidade 6 - Projeto a nível de Sistema}} | |

| − | + | ===Unidade 6 - Projeto a nível de Sistema=== | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | ===Unidade 6 | ||

| − | |||

; Aula 27 (6 Nov): | ; Aula 27 (6 Nov): | ||

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

| Linha 661: | Linha 647: | ||

:* Ver pag. 201 a 208 de <ref name="PEDRONI2010b"/> | :* Ver pag. 201 a 208 de <ref name="PEDRONI2010b"/> | ||

| − | |||

; Aula 29 (12 mai): | ; Aula 29 (12 mai): | ||

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

| Linha 671: | Linha 656: | ||

:* Ver pag. 208 a 213 de <ref name="PEDRONI2010b"/> | :* Ver pag. 208 a 213 de <ref name="PEDRONI2010b"/> | ||

| + | ====ATUAL==== | ||

| + | |||

| + | ;Aula 26 (28 abr): | ||

| + | *Código Sequencial. | ||

| + | * Projeto de relógio HH:MM:SS com conversor para 7 segmentos. Implementar um relógio usando contador de 0 a 9 (BCD). Para implementar o relógio use PROCESS separados para implementar a hora, o minuto e o segundo. O relógio deve contar de 00:00:00 até 23:59:59. Os mostradores de 7 segmentos devem ativados por um PROCESS que converte o número 0 a 9 em bits do código SSD. | ||

| + | :* Ver as limitações do QSIM na simulação de sistemas com longa duração. | ||

| + | :* Apreender o uso do simulador Modelsim | ||

| + | :* Implementar o relógio no kit DE2-115. | ||

| + | |||

| + | <!-- | ||

; Aula 30 (15 mai): | ; Aula 30 (15 mai): | ||

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

| Linha 787: | Linha 782: | ||

:*Uso de '''FUNCTION''' e '''PROCEDURE'''. | :*Uso de '''FUNCTION''' e '''PROCEDURE'''. | ||

::*Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ::*Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

| − | + | --> | |

| + | {{collapse bottom}} | ||

| + | <!-- | ||

===Unidade 7=== | ===Unidade 7=== | ||

; Aula 33 (29 Mai): | ; Aula 33 (29 Mai): | ||

Edição das 07h53min de 16 de novembro de 2017

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

library library_name; use library_name.package)name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

|

| Unidade 3 - Tipos de Dados e Operadores em VHDL | ||

|---|---|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY signed_multiplier IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE type_conv_arch OF signed_multiplier IS

BEGIN

y <= std_LOGIC_VECTOR(SIGNED(a) * SIGNED(b));

END ARCHITECTURE;

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

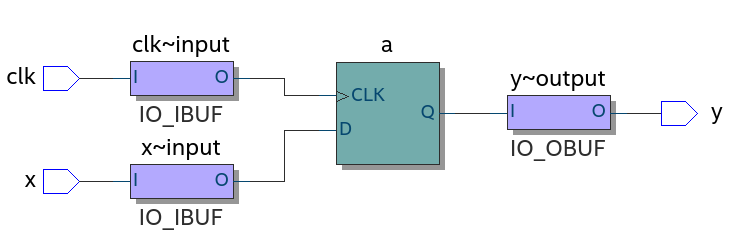

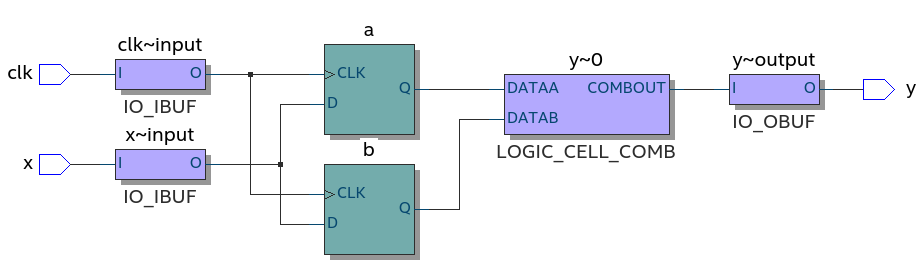

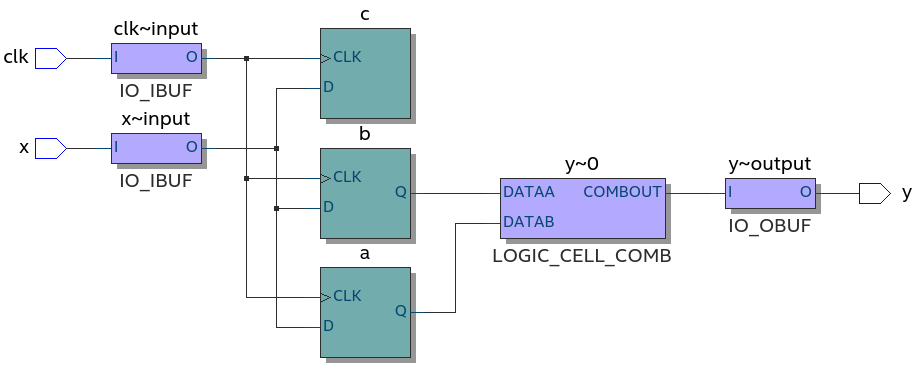

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.  Fig 12. Technology Map do Circuito sem Attribute  Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)  Fig 14. Technology Map do Circuito com Attribute Noprune

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

|

| Unidade 4 - Código Concorrente |

|---|

Unidade 4 - Código Concorrente

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

|

| Unidade 5 - Código Sequencial |

|---|

Unidade 5 - Código Sequencial

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

-- Renomeie a porta rst para rst_in.

PORT (

clk, rst_in : IN BIT;

--Crie um sinal interno para inverter o clock

ARCHITECTURE counter OF slow_counter IS

signal rst : BIT;

BEGIN

rst <= not rst_in;

|

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 6 - Projeto a nível de Sistema

ATUAL

|

Avaliações

- Avaliação A1 - Unidade 2 a 4 (XX/XX/2017) - Local: Lab Redes II.

- Avaliação A2 - Unidade 5 a 7 (XX/XX/2017) - Local: Lab Redes II.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD, e as tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni. Dica use também como fonte de consulta os templates do Quartus.

- Recuperação R1-2 - Unidade 2 a 7 (XX/XX/2017) - Local: Lab Redes II.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma moodle ou email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle

- Autoinscrição na Plataforma Moodle de DLP29006 (engtelecom) - ATENÇÃO! MUDEI O AMBIENTE PARA PRESERVAR O ACESSO DOS ALUNOS ANTERIORES.

| AE0 - Resumo estendido de Artigo (Entrega e Prazo ver Moodle) |

|---|

|

| AE1 - Uso de código concorrente - ALU modificada (Entrega e Prazo ver Moodle) | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

ENTITY alu IS

GENERIC (N: INTEGER := 4); --word bits

PORT (

A, B: IN STD_LOGIC_VECTOR (N-1 DOWNTO 0);

OPCODE: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

ERRO: OUT STD_LOGIC;

Y: OUT STD_LOGIC_VECTOR (N-1 DOWNTO 0));

END ENTITY;

|

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

| EL0 - Resolução dos exercícios do Cap 2 |

|---|

especificado.

---------------------------------------

-- File: mux.vdh

---------------------------------------

-- Declaração das Bibliotecas e Pacotes

--

LIBRARY ieee;

USE _________________________ ;

---------------------------------------

-- Especificação das entradas e saídas e nome da ENTITY

ENTITY mux IS

PORT (

__ , __ : ___ STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____________________________ ;

___ : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END _____ ;

---------------------------------------

ARCHITECTURE example OF _____ IS

BEGIN

PROCESS (a, b, ____ )

BEGIN

IF (sel = "00") THEN

c <= "00000000";

ELSIF (__________) THEN

c <= a;

_____ (sel = "10") THEN

c <= __;

ELSE

c <= (OTHERS => '__');

END ___ ;

END _________ ;

END _________ ;

---------------------------------------

|

| EL1 - Uso de tipos de dados e operadores |

|---|

|

| EL2 - Resolução dos exercícios do Cap 3 |

|---|

|

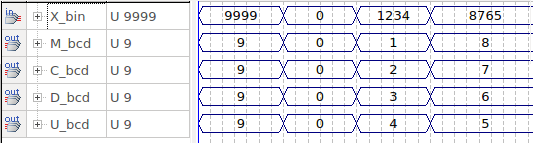

| AR2- Conversor de Binário para BCD |

|---|

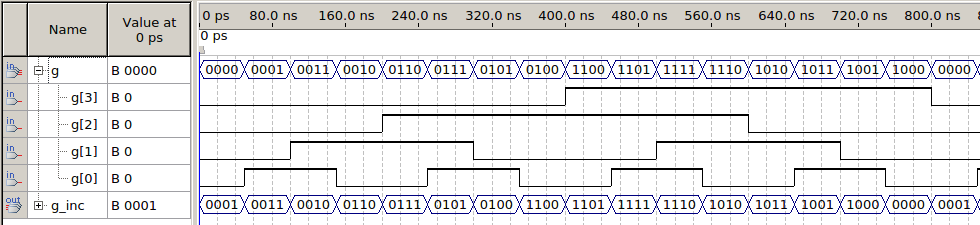

Fig. 20 - Simulação da conversão de binário para BCD

entity bin2bcd is

port (

X_bin : in std_logic_vector(13 downto 0); -- 000 a 999

C_bcd : out std_logic_vector(3 downto 0); -- Centena

D_bcd : out std_logic_vector(3 downto 0); -- Dezena

U_bcd : out std_logic_vector(3 downto 0)); -- Unidade

end entity;

architecture example of bin2bcd is

--declaração de sinais auxiliares

begin

--descrição do hardware

end architecture;

M_bcd <= std_logic_vector(to_unsigned(M,4)); |

| EL4 - Resolução dos exercícios do Cap 4 |

|---|

|

| EL5 - Resolução dos exercícios do Cap 5 |

|---|

|

| AR3 - Unidade somadora e subtratora |

|---|

onde são respectivamente valores numéricos positivos e negativos.

|

| EL6 - Resolução dos exercícios do Cap 6 |

|---|

|

Referências Bibliográficas:

- ↑ PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335