Mudanças entre as edições de "DIG222802 2017 1 AULA08"

| Linha 19: | Linha 19: | ||

#CI 555 | #CI 555 | ||

| − | #R<sub>1</sub>=R<sub>2<sub>=10k ohms. | + | #R<sub>1</sub>=R<sub>2</sub>=10k ohms. |

#C=47uF | #C=47uF | ||

#Capacitor de 10nF (filtro). | #Capacitor de 10nF (filtro). | ||

Edição das 13h13min de 17 de abril de 2017

Laboratório 3

O TERCEIRO experimento da turma de Digital 2 da Engenharia vai ser realizado no LabMIC (Sala 104) entre 13h30min e 15h20min e 15h40min e 17h30min. Vamos testar um contador/registrador em anel utilizando um circuito com quatro flip-flops tipo D. O experimento está dividido em três etapas: A primeira trata-se de um circuito gerador de clock com o CI 555, a segunda parte, montar um registrador em anel com dois circuitos integrados 7474, mostrando o resultado das quatro saídas nos LEDs disponíveis na bancada digital. A terceira e última parte, aproveitando o mesmo esquema do circuito, implementar o contador/registrador Jonhson.

Parte 1

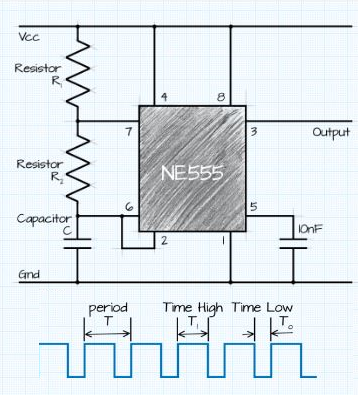

O circuito do oscilador 555 no modo astável produz ondas quadradas, oscilando entre 0V e VCC. A configuração do astável está demonstrado abaixo:

Lista de componentes

- CI 555

- R1=R2=10k ohms.

- C=47uF

- Capacitor de 10nF (filtro).

Parte 2

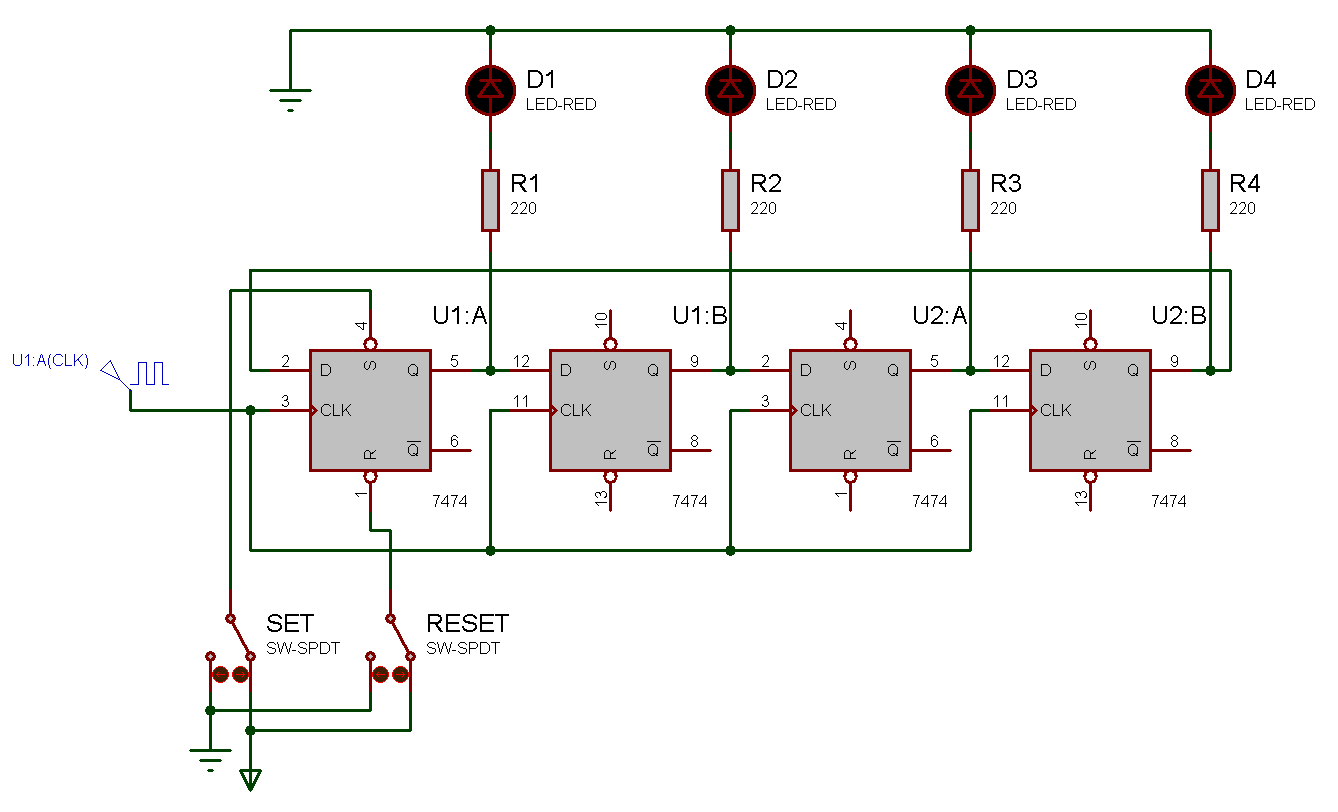

- Objetivo

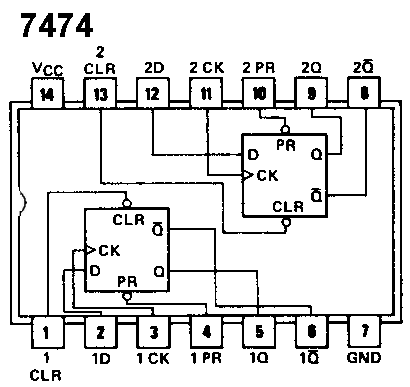

- Montar um contador/registrador em anel de 4 bits, utilizando CI 7474, chaves de RESET e SET no primeiro FF e apresentar o resultado das quatro saídas nos de LEDs. O circuito correspondente é apresentado na Figura 1.

Figura 1 - Registrador em anel de 4 bits.

Procedimento

- Formar até 10 equipes com 2 integrantes;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Testar o funcionamento do gerador de frequência da bancada digital, se não estiver funcionando, pode-se utilizar uma chave como clock (manual);

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND;

- Fazer a ligação de SET e RESET de um dos FF nas chaves seletoras;

- Fazer a ligação, se necessário, do SET e RESET em VCC. Lembrando que esta porta é ativo baixo;

- Fazer a ligação entre as portas lógicas dos CIs;

- Fazer a ligação de clock com gerador de frequência de 1Hz, ou colocando numa chave seletora;

- Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando.

Poderá haver algumas ligações (extras) de outros pinos em VCC/GND não detectadas na simulação.

Parte 3

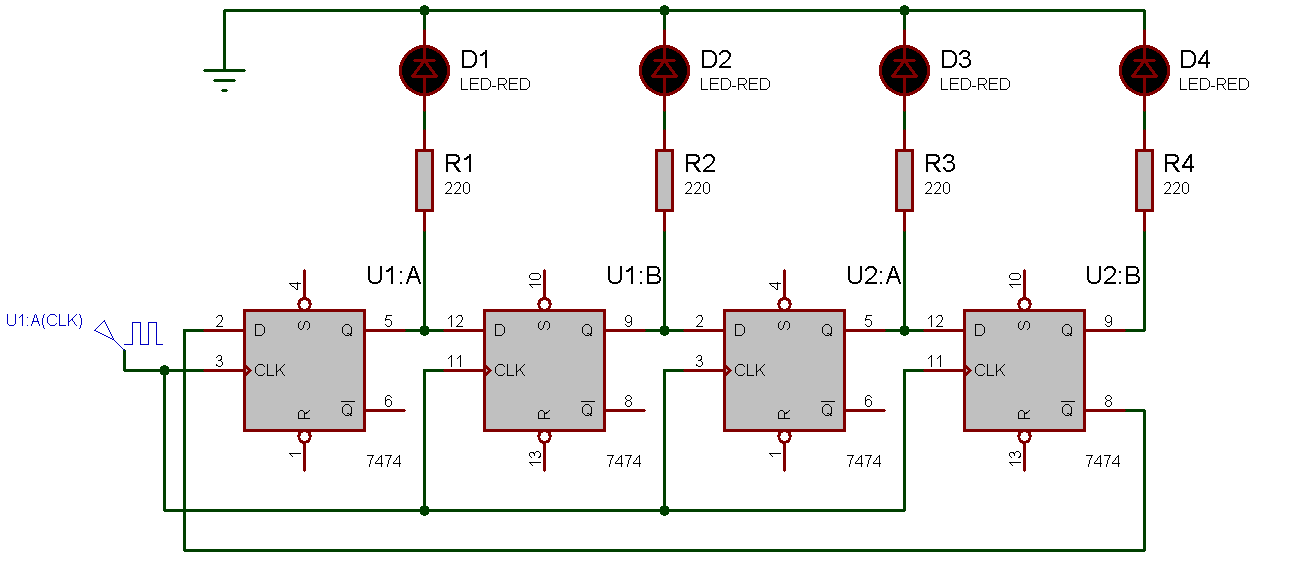

- Objetivo

- Alterar o circuito do contador em anel para que ele funcione como contador Jonhson, comprovando seu funcionamento. O circuito é visto da Figura 2.

Figura 2 - Contador Jonhson.

Procedimento

- Mesmas equipes;

- Repetir as ligações utilizando o parte do esquemático dos CIs já realizado;

- Desfazer as ligações do SET e RESET do primeiro FF ligando-os em VCC se necessário;

- Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando.

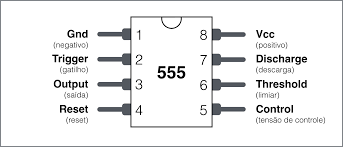

Circuito

Figura 3 - Esquemático do CI 7474 - Dois FF tipo D.

Material Utilizado

- Oscilador

- CI 555

- Resistor 100k

- Resistor 1M

- Capacitor de 560nF

- Capacitor de 15nF

- Registrador

- CI 7474

Relatório

O relatório simplificado deverá ser entregue até às 18h de amanhã (quarta-feira dia 19/10).

- Critérios avaliativos

- Montagem: 4 (+1+1+1+1)

- Escrita (coerente e conclusiva): 6

Referências

[1] CASAGRANDE, Jorge H. B.. Apostila: ELETRÔNICA DIGITAL 1 CAPÍTULO 3 – Circuitos Combinacionais. CEFET/SC, 2005.

[2] http://labdegaragem.com/profiles/blogs/ci-555-modo-astavel-oscilador