# Eletrônica Digital I (EDL I)

- Instituto Federal de Educação, Ciência e Tecnologia

- de Santa Catarina Campus São José

- Prof. Glauco Cardozo

- glauco.cardozo@ifsc.edu.br

Os circuitos lógicos dos sistemas digitais podem ser de dois tipos:

- circuitos combinacionais

- circuitos seqüenciais

Um circuito combinacional é constituído por um conjunto de portas lógicas as quais determinam os valores das saídas diretamente a partir dos valores atuais das entradas, realizando um processamento a partir de um conjunto de equação booleanas.

Um circuito seqüencial, por sua vez, emprega elementos de armazenamento denominados latches e flipflops, além de portas lógicas. Os valores das saídas do circuito dependem dos valores das entradas e dos estados dos latches ou flip-flops utilizados.

#### Circuitos Combinacionais de Interconexão

- Decodificadores

- Seletores

#### Circuitos Aritméticos

- Meio somador

- Somador Completo

- O somador paralelo

- O multiplicador

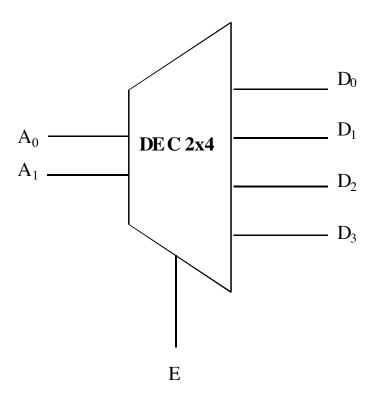

#### **Decodificadores**

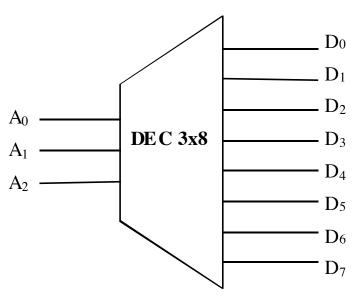

Um decodificador é um circuito combinacional usado para ativar ou habilitar um (e somente um) dentre m componentes. É assumido que cada componente possui um índice entre 0 e m-1, representado por um endereço em binário.

#### **Decodificadores**

Um decodificador é um circuito combinacional usado para ativar ou habilitar um (e somente um) dentre m componentes. É assumido que cada componente possui um índice entre 0 e m-1, representado por um endereço em binário.

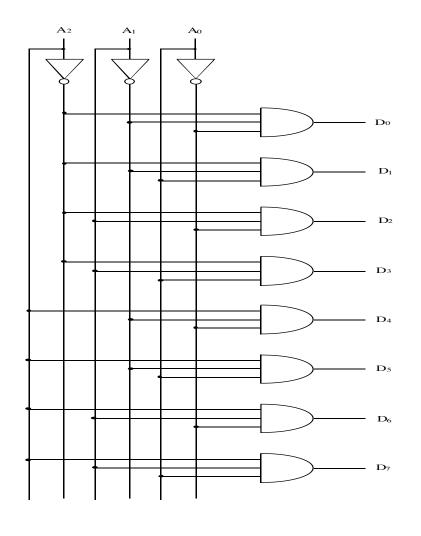

No caso de um decodificador 3:8, serão 8 saídas, onde cada saída pode ser encarada como um endereço diferente. Para ativar uma dentre 8 saídas são necessárias 3 variáveis de entrada (daí 3:8).

### **Decodificadores**

| endereço | Entradas (sinais de controle) |       |       | saídas |       |       |       |       |       |       |       |

|----------|-------------------------------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|

|          | $A_2$                         | $A_1$ | $A_0$ | $D_0$  | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ |

| 0        | 0                             | 0     | 0     | 1      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1        | 0                             | 0     | 1     | 0      | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 2        | 0                             | 1     | 0     | 0      | 0     | 1     | 0     | 0     | 0     | 0     | 0     |

| 3        | 0                             | 1     | 1     | 0      | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

| 4        | 1                             | 0     | 0     | 0      | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 5        | 1                             | 0     | 1     | 0      | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 6        | 1                             | 1     | 0     | 0      | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

| 7        | 1                             | 1     | 1     | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

### **Decodificadores**

#### **Decodificadores**

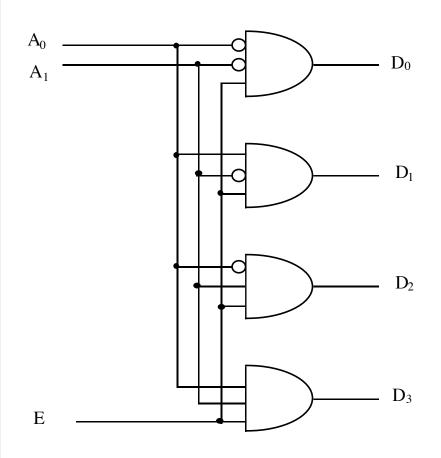

Um decodificador pode possuir uma entrada de habilitação (enable, em inglês). Esta entrada tem a função de habilitar ou desabilitar seu funcionamento.

| saídas<br>desabilitadas |

|-------------------------|

| desabilitadas           |

|   | endereço | (sina | entradas<br>is de con |       | saídas |       |       |       |  |

|---|----------|-------|-----------------------|-------|--------|-------|-------|-------|--|

|   |          | Е     | $A_1$                 | $A_0$ | $D_0$  | $D_1$ | $D_2$ | $D_3$ |  |

| _ | -        | 0     | 0                     | 0     | 0      | 0     | 0     | 0     |  |

|   | -        | 0     | 0                     | 1     | 0      | 0     | 0     | 0     |  |

|   | -        | 0     | 1                     | 0     | 0      | 0     | 0     | 0     |  |

| / | -        | 0     | 1                     | 1     | 0      | 0     | 0     | 0     |  |

|   | 0        | 1     | 0                     | 0     | 1      | 0     | 0     | 0     |  |

|   | 1        | 1     | 0                     | 1     | 0      | 1     | 0     | 0     |  |

|   | 2        | 1     | 1                     | 0     | 0      | 0     | 1     | 0     |  |

|   | 3        | 1     | 1                     | 1     | 0      | 0     | 0     | 1     |  |

#### **Decodificadores**

Um decodificador pode possuir uma entrada de habilitação (enable, em inglês). Esta entrada tem a função de habilitar ou desabilitar seu funcionamento.

|                 | endereço entradas (sinais de controle) |   |       | saídas |       |       |       |       |

|-----------------|----------------------------------------|---|-------|--------|-------|-------|-------|-------|

| saídas          |                                        | Е | $A_1$ | $A_0$  | $D_0$ | $D_1$ | $D_2$ | $D_3$ |

| desabilitadas—— | <b>-</b>                               | 0 | X     | X      | 0     | 0     | 0     | 0     |

|                 | 0                                      | 1 | 0     | 0      | 1     | 0     | 0     | 0     |

|                 | 1                                      | 1 | 0     | 1      | 0     | 1     | 0     | 0     |

|                 | 2                                      | 1 | 1     | 0      | 0     | 0     | 1     | 0     |

|                 | 3                                      | 1 | 1     | 1      | 0     | 0     | 0     | 1     |

### **Decodificadores**

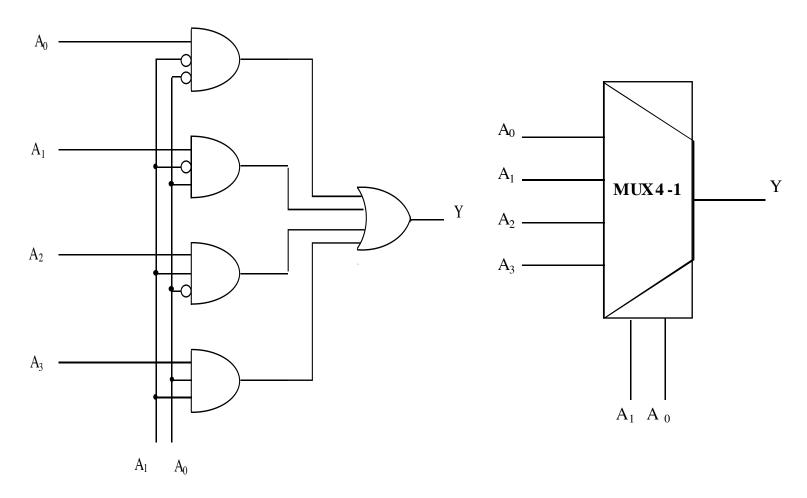

#### **Seletores**

Um seletor (também conhecido como multiplexador) é um circuito combinacional usado para **selecionar** uma dentre um conjunto de m fontes de informação disponíveis.

#### **Seletores**

Dado o conjunto de entradas A0, A1, A2 e A3, e as variáveis de seleção S0 e S1, a tabela verdade para um seletor 4-1 será:

| endereço | variáv<br>sele | saída |       |

|----------|----------------|-------|-------|

|          | $S_1$          | $S_0$ | Y     |

| 0        | 0              | 0     | $A_0$ |

| 1        | 0              | 1     | $A_1$ |

| 2        | 1              | 0     | $A_2$ |

| 3        | 1              | 1     | $A_3$ |

$$Y = \overline{S_0} \cdot \overline{S_1} \cdot A_0 + \overline{S_0} \cdot S_1 \cdot A_1 + S_0 \cdot \overline{S_1} \cdot A_2 + S_0 \cdot S_1 \cdot A_3$$

### **Seletores**

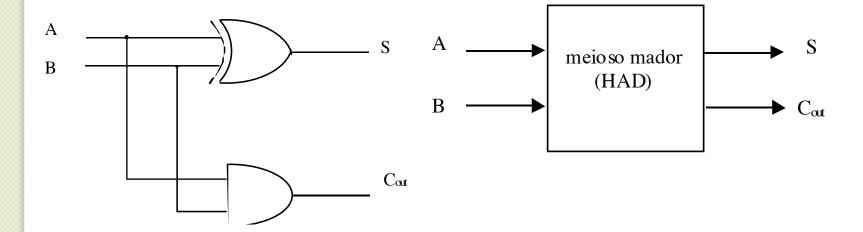

#### Meio somador

Considerando-se todas as 4 combinações de valores que podem ocorrer, os resultados possíveis dessa adição são:

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 0 = 1$

$1 + 1 = 10$

| A | В | Cout | S |

|---|---|------|---|

| 0 | 0 | 0    | 0 |

| 0 | 1 | 0    | 1 |

| 1 | 0 | 0    | 1 |

| 1 | 1 | 1    | 0 |

transporte de saída (carry out)

#### Meio somador

Considerando-se todas as 4 combinações de valores que podem ocorrer, os resultados possíveis dessa adição são:

$$S = \overline{A}.B + A.\overline{B} = A \oplus B$$

$$Cout = A \cdot B$$

### **Somador completo**

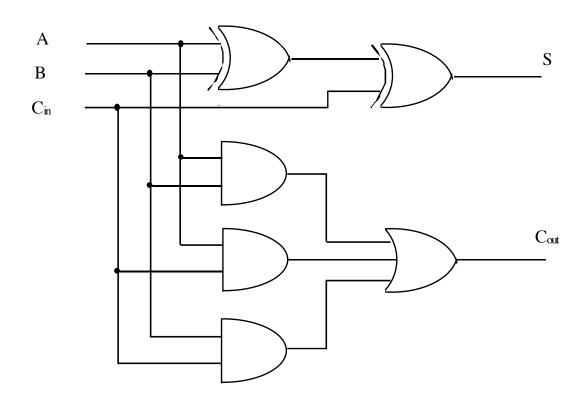

O circuito capaz de realizar a soma de três bits (A, B e Cin), gerando o resultado em dois bits (S e Cout) é denominado **somador completo** (full adder)

| A | В | Cin | Cout | S |

|---|---|-----|------|---|

| 0 | 0 | 0   | 0    | 0 |

| 0 | 0 | 1   | 0    | 1 |

| 0 | 1 | 0   | 0    | 1 |

| 0 | 1 | 1   | 1    | 0 |

| 1 | 0 | 0   | 0    | 1 |

| 1 | 0 | 1   | 1    | 0 |

| 1 | 1 | 0   | 1    | 0 |

| 1 | 1 | 1   | 1    | 1 |

### **Somador completo**

$$S = \overline{A} \cdot \overline{B} \cdot C_{\text{in}} + \overline{A} \cdot B \cdot \overline{C_{\text{in}}} + A \cdot \overline{B} \cdot \overline{C_{\text{in}}} + A \cdot B \cdot C_{\text{in}} = A \oplus B \oplus C_{\text{in}}$$

$$C_{out} = A \cdot B + A \cdot C_{in} + B \cdot C_{in}$$

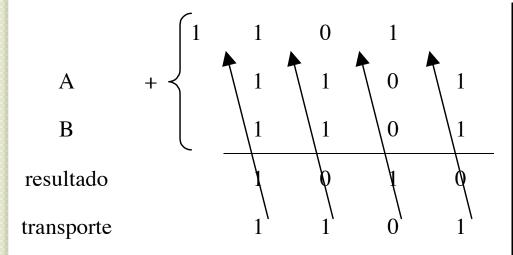

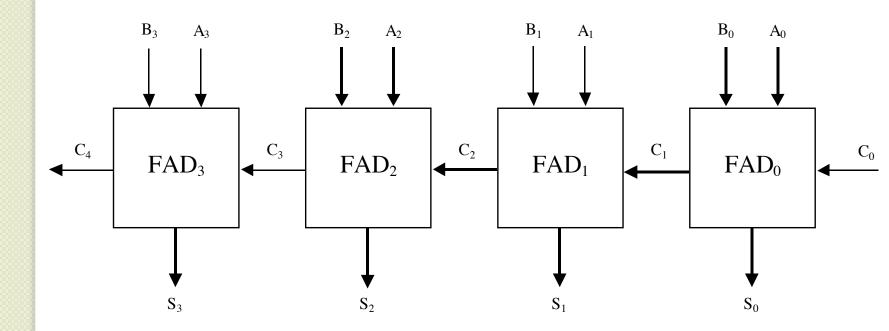

### Somador paralelo tipo ripple carry

Utilizando-se n somadores completos, pode-se realizar um somador capaz de operar dois números binários de n bits

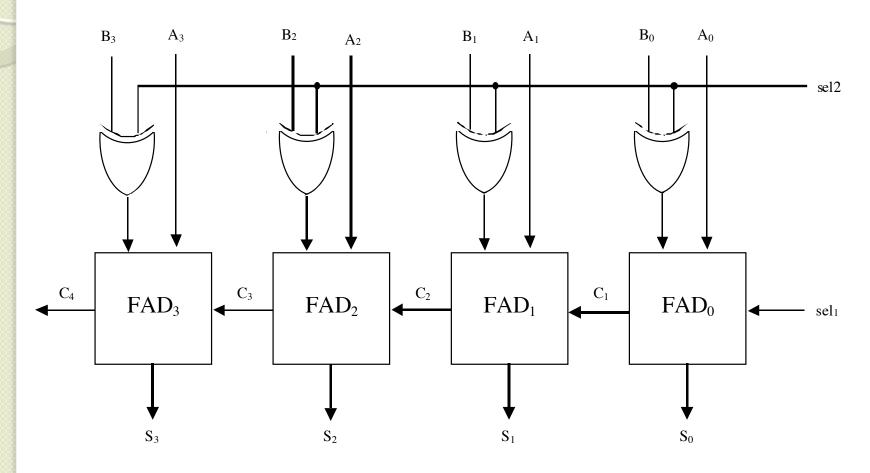

#### Somador/subtrator

A subtração de dois números inteiros em binário pode ser feita utilizando-se a seguinte fórmula:

$$A - B = A + \overline{B} + 1$$

Esse circuito é originado do somador paralelo de 4 bits, porém com a adição de portas xor nas entradas associadas a B, de modo a permitir a negação individual de cada bit de B.

#### Somador/subtrator

### Somador/subtrator

| sel <sub>2</sub> | sel <sub>1</sub> | operação                   | descrição                                     |

|------------------|------------------|----------------------------|-----------------------------------------------|

| 0                | 0                | S = A + B + 0              | adiciona $A \in B (S = A + B)$                |

| 0                | 1                | S = A + B + 1              | adiciona A e B incrementado $(S = A + B + 1)$ |

| 1                | 0                | $S = A + \overline{B} + 0$ | subtrai B decrementado de A $(S = A - B - 1)$ |

| 1                | 1                | $S = A + \overline{B} + 1$ | subtrai B de A (S = A - B)                    |

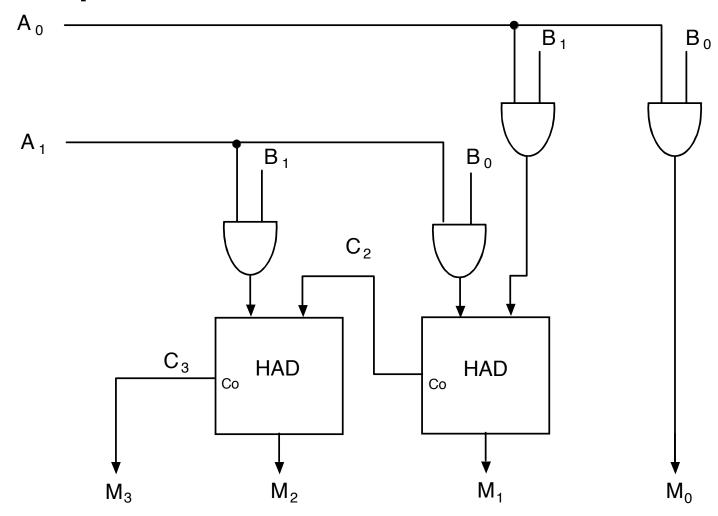

### Multiplicador

A multiplicação de números binários é realizada da mesma maneira como a de números decimais.

|   |       |           | $\mathrm{B}_1$ | $\mathrm{B}_0$ | ← multiplicando   |

|---|-------|-----------|----------------|----------------|-------------------|

| × |       |           | $A_1$          | $A_0$          | _ ← multiplicador |

| _ | $C_3$ | $C_2$     |                |                | ← transportes     |

| + |       |           | $A_0 B_1$      | $A_0 B_0$      |                   |

|   |       | $A_1 B_1$ | $A_1 B_0$      | _              |                   |

| - | $M_3$ | $M_2$     | $M_1$          | $M_0$          | -<br>← resultado  |

### Multiplicador

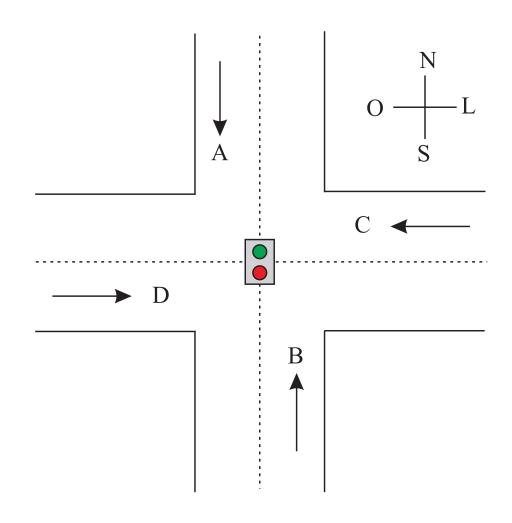

### Exercício (Semáforo)

Projete um sistema de sinalização de transito para o cruzamento mostrado na Fi- gura 6.1. Sensores detectores de veículos são colocados ao longo das pistas C e D (na Rodovia) e nas pistas A e B (via de acesso). As saídas desses sensores serão nível BAIXO (0) quando nenhum veículo estiver presente e nível alto ALTO (1) quando um veículo estiver presente. O sinal de trânsito no cruzamento é controlado de acordo com a seguinte lógica:

Exercício (Semáforo)

- Exercício (Semáforo)

- O sinal da direção leste-oeste (L-O) será verde quando as duas pistas C e D estiverem ocupadas.

- O sinal da direção leste-oeste será verde sempre que as pistas C ou D estiverem ocupadas, mas com as pistas A e B desocupadas.

- O sinal da direção norte-sul (N-S) será verde sempre que as duas pistas A e B estiverem ocupadas, mas as C e D estiverem desocupadas.

- O sinal da direção norte-sul também será verde quando as pistas A ou B estiverem ocupadas enquanto ambas as pistas C e D estiverem vazias.

- O sinal da direção leste-oeste será verde quando não houver veículo presente.

- Exercício (Semáforo)

- As entradas do sistemas são os sinais dos sensores A, B, C e D, e o circuito lógico terá duas saídas NS e LO, uma para cada semáforo, cujo nível ALTO ocorrerá quando houver a luz verde.

- Apresente no desenvolvimento do projeto, a tabela verdade, mapa de Karnaugh expressões lógicas e diagrama lógico.

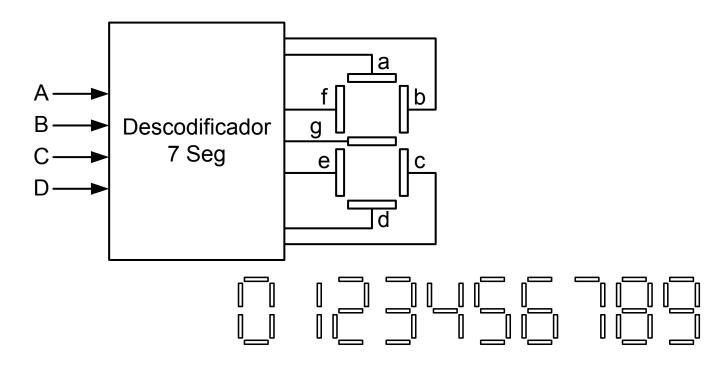

### Exercício (7 segmentos)

Considere-mos que se pretende realizar um circuito denominado descodificador (circuito de n entradas que produz k saídas com k>n) de 7 segmentos.

### Exercício (7 segmentos)

O circuito descodificador tem quatro variáveis de entrada e produz sete variáveis de saídas com o comportamento que a seguir se descreve. A cada uma das saídas do descodificador está associada um segmento de um mostrador no qual é possível desenhar todos algarismos entre 0 e 9. Admitamos que as variáveis de entrada são geradas por um sistema electromecânico, que só gera 10 combinações, ou seja, o descodificador não é sujeito às 16 (24) possíveis combinações das quatro variáveis.

### Exercício (7 segmentos)

Esta especificação vai trazer um novo conceito na simplificação das funções de saída, pois leva a que o projectista não tenha que contemplar no projecto, qual a reacção do descodificador quando sujeito às restantes combinações. Estas combinações são designadas de don't care (não importa) e são representadas no mapa de Karnaugh com o símbolo (-) ou(x). Como o termo mínimo assim assinalado corresponde a um valor lógico por definir, então ele poderá ser associado aos l's no sentido de criar um termo mais simples, caso contrário será tomado como lógico 0.

Exercício (7 segmentos)

Apresente no desenvolvimento do projeto, a tabela verdade, mapa de Karnaugh expressões lógicas e diagrama lógico.